基础知识 QEMU 架构

QEMU 与 KVM 的完整架构整体上分为三大部分:

VMX root 模式的用户空间应用层 (QEMU 进程)VMX root 模式的内核空间 (Linux KVM 驱动模块)VMX non-root 模式的虚拟机运行环境 (Guest 虚拟机)

其中,VMX root 和 VMX non-root 是 CPU 支持硬件虚拟化指令集(Intel 的 VT-x 技术)之后引入的两个模式:

VMX root 模式 用于宿主机系统(即运行虚拟化软件的 Host),在该模式下可执行特权虚拟化指令,完整控制 CPU 虚拟化行为。VMX non-root 模式 用于运行客户机(即 Guest OS),Guest 在 non-root 模式下正常运行,绝大部分指令可直接由物理 CPU 执行。特殊敏感操作会导致 CPU 从 non-root 模式退出到 root 模式(VM-Exit),交由 KVM/QEMU 处理。

无论 VMX root 还是 VMX non-root 模式,都包含 ring 0 到 ring 3 共 4 个特权级别。

QEMU 进程 在 QEMU 与 KVM 虚拟化架构中,QEMU 进程位于 VMX root 模式的用户空间,承担如下任务:

初始化虚拟机硬件环境 :

创建虚拟芯片组(如 PCI 主桥、内存控制器)

根据用户启动参数 (-device 等) 创建并初始化各类虚拟设备(如磁盘、网卡、显卡、输入设备)

分配并管理来宾(Guest)物理内存空间,QEMU 将 Guest 的物理内存映射到宿主机进程虚拟地址空间中(使用 mmap 等系统调用)。

设备模拟与 IO 请求处理 :

设备 IO 请求事件 :当虚拟机对虚拟设备发起 IO 请求(PIO/MMIO)并触发 VM-Exit 后,KVM 会通过 ioctl 接口通知 QEMU 处理这些事件。管理命令事件 :如用户通过 QEMU 的管理界面或 QMP(QEMU Machine Protocol)发送的命令。宿主机设备事件 :如网络数据接收或宿主设备状态变化(例如 tap 网络设备的数据包到达),QEMU 会做出响应并模拟设备行为。

对于虚拟机设备 IO 访问事件,QEMU 用户空间通过预先注册的 MemoryRegionOps 等设备模型回调函数完成 IO 请求处理,模拟真实硬件的行为(例如返回设备寄存器值、进行 DMA 操作、发起中断请求)。

CPU 线程管理 :

虚拟机 (Guest) 环境 Guest OS 在 VMX non-root 模式下运行,有自己的应用层和内核层:

对 Guest OS 而言,QEMU 和 KVM 完全透明 ,不需要对 Guest OS 做任何修改,就可以在虚拟机中正常运行。

Guest 虚拟机的每个 vCPU 对应宿主机中 QEMU 进程的一个线程。通过 KVM 和宿主 OS 调度,这些线程能直接在物理 CPU 上执行 Guest 代码。

Guest 虚拟机内存通过两层映射实现地址转换:

GVA→GPA (Guest 虚拟地址 → Guest 物理地址):由虚拟机自身 OS 页表管理。GPA→HPA (Guest 物理地址 → Host 物理地址):由 KVM 驱动维护的 Extended Page Tables (EPT) 或 Shadow 页表完成。

Guest OS 中的设备通过 QEMU 呈现,Guest OS 在启动时进行设备枚举并加载相应的设备驱动程序。

Guest OS 运行中,通过 IO 端口 (PIO) 或内存映射 IO (MMIO) 与设备进行交互时,KVM 会截获这些敏感操作(VM-Exit)并将请求分发至 QEMU 用户空间,由 QEMU 负责处理这些设备请求。

KVM 内核驱动 KVM 驱动位于 VMX root 模式的 Linux 内核空间,以 misc 设备驱动形式 (/dev/kvm) 存在,提供如下功能:

QEMU 虚拟化 CPU 虚拟化 vCPU 创建与初始化 QEMU 为每个 vCPU 启动一个线程,使用 /dev/kvm 的 ioctl 建立虚拟机/虚拟 CPU:KVM_CREATE_VM → KVM_CREATE_VCPU → mmap(KVM_RUN) → KVM_SET_REGS/SET_SREGS/SET_MSRS …

执行循环与 VM-Exit/Entry vCPU 线程反复 ioctl(KVM_RUN) 进入来宾(VM-Entry)。当发生敏感事件/条件 时硬件触发 VM-Exit 返回宿主:struct kvm_run,QEMU读出后分发处理(设备回调、注入中断、继续运行等),随后再次 KVM_RUN(VM-Entry)。

简化伪码:

1 2 3 4 5 6 7 8 9 for (;;) { ioctl(vcpu_fd, KVM_RUN); switch (run->exit_reason) { case KVM_EXIT_MMIO: qemu_mmio_dispatch(run->mmio); break ; case KVM_EXIT_IO: qemu_pio_dispatch(run->io); break ; case KVM_EXIT_HLT: break ; } }

VMCS/VMCB Intel VT-x 使用 VMCS 保存每个 vCPU 的来宾/宿主状态(AMD SVM 对应 VMCB )。这不是“像系统调用那样的内核栈切换”,而是硬件虚拟化态切换 :VM-Entry/Exit 时由 CPU 在 VMCS/VMCB 与宿主状态之间来回装载。

内存虚拟化 1 2 3 4 5 6 Guest process Guest kernel QEMU (userspace) Host kernel (KVM) DRAM GVA ──►(guest PT)──► GPA ──►(EPT/NPT)──► HPA (HVA 仅用于用户态管理/拷贝) │ │ ▲ │ └─MMIO(未映射/设备型)───┘ ← VM-Exit → QEMU MemoryRegionOps 回调 │ └─IOVA(可选, 有vIOMMU时)──►(vIOMMU映射)──►GPA───►(EPT/NPT)──►HPA

内存地址类别

GVA(Guest Virtual Address) :来宾进程看到的虚拟地址,受来宾内核维护的页表(CR3 指向的页表根)管理。GPA(Guest Physical Address) :来宾眼中的“物理地址”,由来宾内核分配/管理,实际上只是一个客户机物理地址空间 。HVA(Host Virtual Address) :宿主机用户态(QEMU 进程)的虚拟地址,QEMU 用 mmap() 得到,用来承载来宾的“物理内存”数据 。HPA(Host Physical Address) :宿主机真实物理地址。

真正跑指令的“硬件级地址翻译”,根本不认识 HVA 。

CPU 在来宾里做访存时,只走这条链路:

GVA(来宾虚拟) →【来宾页表】→ GPA(来宾物理) →【EPT/NPT(二级页表)】→ HPA(宿主物理)

HVA(Host Virtual Address)只是QEMU 这个用户态进程里的指针 ,给 QEMU/KVM 在“管理阶段/缺页处理/用户态拷贝”用的,不在硬件翻译链路里 。

内存结构初始化

QEMU 分配宿主用户态内存

通过 mmap()(或基于 hugetlbfs 的文件、匿名内存、memfd 等后端)在 QEMU 进程地址空间 中创建一段连续的 HVA 区域,作为“来宾物理内存”的承载。

QEMU 维护 MemoryRegion/AddressSpace

QEMU 的 Memory API 将 RAM 区域与 I/O 区域抽象成 MemoryRegion,并组合成来宾的 GPA 地址空间布局。

告知 KVM:内存槽(memslot)

QEMU 通过 KVM_SET_USER_MEMORY_REGION ioctl 把若干段 GPA 区间 与它们对应的 HVA 起始地址 与大小注册到 KVM,形成 memslot 。

一个 memslot 的关键信息包含:slot 编号、guest_phys_addr(GPA 起始)、memory_size、userspace_addr(HVA 起始)、flags(如脏页记录)。

memslot 数量有内核能力限制(KVM_CAP_NR_MEMSLOTS 暴露具体上限,一般为数百级 ),生产中通常合并为少量大区域,便于管理与迁移。

动态更新

QEMU 之后若调整内存布局(热插拔、I/O BAR 映射变化等),会再次调用 KVM_SET_USER_MEMORY_REGION 更新 memslot,KVM 以 SRCU 等机制保证并发安全。

内存地址转换 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 Guest' processes +--------------------+ Virtual addr space | | +--------------------+ | | \__ Page Table \__ \ \ | | Guest kernel +----+--------------------+----------------+ Guest's phy. memory | | | | +----+--------------------+----------------+ | | \__ \__ \ \ | QEMU process | +----+------------------------------------------+ Virtual addr space | | | +----+------------------------------------------+ | | \__ Page Table \__ \ \ | | +----+-----------------------------------------------++ Physical memory | | || +----+-----------------------------------------------++

来宾页表:GVA → GPA

由来宾 OS 自己维护(gCR3 指向的页表),机制与真机一致(4K/2M/1G 页、LA57、SMEP/SMAP 等)。

二级页表(硬件/KVM):GPA → HPA

Intel:EPT ,AMD:NPT 。支持 4K/2M/1G 二级页,通常选 Write-Back 内存类型。

当 GPA 首次触达或权限不满足时会发生 EPT/NPT violation (或缺页),触发 VM-Exit ,KVM/内核再建立/修正映射后重新进入来宾。

当来宾系统 执行一条内存访问指令 时,通常会有如下过程:

快路径:TLB 命中(硬件一步到位)

当同一地址最近访问过、TLB 里已经有“合成后的”条目时,CPU 在来宾里执行:GVA ──TLB命中──► HPA → 直接读/写 DRAM

这条 TLB 记录其实是“GVA→HPA 的组合结果”(包含了两段翻译的缓存),所以不需要再查页表,也不会 VM-Exit 。

HVA 完全没出现 ;硬件不认识它。

慢路径(第一次访问 / TLB 未命中)

TLB miss 时,硬件要做“两段式翻译”。注意:连“读来宾页表本身”的每一步,也要经过 EPT/NPT 。

来宾页表把 GVA → GPA (仍在 VMX non-root,硬件完成)

以 x86-64 四级页表为例(PML4→PDPT→PD→PT),硬件做:

读 gCR3 得到来宾页表根(一个 GPA );

依次读 PML4E、PDPTE、PDE、PTE——这些表项都存放在“来宾物理内存”里 ,所以每次读表项(用到 GPA)又会通过下一步 EPT 去取对应的 HPA ;

得到最终 GPA (或大页的 GPA)。

如果某一级表项 不存在/权限不符 ,CPU在来宾内部 触发 #PF(页错误) ,交给来宾内核处理(仍在 non-root,不会到 KVM,除非你特意设置拦截)。

二级页表把 GPA → HPA (需要则 VM-Exit)

硬件用 VMCS/VMCB 里的 EPTP/NPT 做二级翻译:

至此你能看到:硬件真正访存只到 HPA 。HVA 只在 KVM 建/改 EPT 的那一刻被用作“找到那个物理页”的线索 ,和 QEMU 用户态做 memcpy() 时当作普通指针使用。

外设虚拟化 QEMU 里外设虚拟化的目标是:让 Guest 看到“像真的”设备,并在功能、性能、可迁移性 之间取舍。控制面靠 PIO/MMIO ,数据面靠 DMA ;运行时遇到设备访问会 VM-Exit→QEMU(或快路径) 处理。

QEMU 外设虚拟化的实现方式主要有三种:

纯模拟(QEMU device model) :设备寄存器以 PIO/MMIO 暴露;每次访问 VM-exit → QEMU 回调处理。准虚拟(virtio 家族) :以 virtqueue 共享环传数据,显著减少陷入;数据面可下沉到 vhost(内核) 或 vhost-user(外部进程,如 DPDK/SPDK/virtiofsd) ,或用 vDPA 由硬件/内核直接跑。直通(VFIO,含 SR-IOV/VF) :设备直接给 VM,用 IOMMU 做 DMA 隔离,性能接近裸机;

中断虚拟化 中断控制器 中断控制器主要有两种:

Intel 8259(PIC) :传统单处理器时代的可编程中断控制器(通过 IRQ0–IRQ15)。I/O APIC + LAPIC :SMP 时代的主流组合:

IOAPIC :芯片组侧把外设中断路由到 CPU 逻辑中断向量。LAPIC :每个 vCPU 上的本地 APIC,负责接收/投递中断;x2APIC 模式用 MSR 代替 MMIO,访问更快、向量空间更大。

QEMU 支持既能用户态模拟 8259/IOAPIC/LAPIC,也能调用 KVM 的 in-kernel irqchip 在内核中模拟,以减少 VM-Exit。对应的命令行(x86):-machine kernel-irqchip=on|off|split

on:8259/IOAPIC/LAPIC 全部在内核模拟(性能最佳,推荐 )。off:全部由 QEMU 用户态模拟(易调试,性能最低 )。split:通常是 LAPIC 在内核、IOAPIC/PIC 在用户态 ,用于兼容/迁移场景(行为依平台/版本)。

中断类型 中断有三种类型的虚拟化:

类型

触发方式

经手的控制器

特性

适用

INTx 电平触发线(INTA~D),共享

IOAPIC → LAPIC (可能先过 PIC)可能“黏线”,必须 EOI 撤线;易抖动

兼容保底

MSI 设备写一条内存消息 (MSI addr/data)

直达 LAPIC 向量少,已优于 INTx

老驱动/设备

MSI‑X 同 MSI,但每队列独立条目

直达 LAPIC 多向量 (队列一对一),最稳最快强烈推荐 (网/块多队列)

INTx,且 kernel-irqchip=off(全在 QEMU,最慢)

Raise :QEMU 仿真设备调用 pci_set_irq(dev, level=1) 提出中断。Route :QEMU 修改虚拟 IOAPIC 的重定向表(目标 vCPU、触发方式、向量)。Deliver :QEMU 通过 KVM 的 ioctl 把中断注入到 vCPU(用户态切内核,再切到 vCPU)EOI :来宾在 LAPIC 写 EOI → VM‑Exit 到 QEMU → QEMU 更新 LAPIC/IOAPIC 状态 → 再回到 vCPU。性能最差 。

INTx,且 kernel-irqchip=on(全在内核,快很多)

Raise :

QEMU 仿真设备可以直接通过 irqfd 把一个 eventfd 绑到 GSI;设备一触发就把 eventfd 写 1。

KVM 内核 irqchip 收到 eventfd → 内核里 更新 IOAPIC/PIC 状态。

Route/Deliver :内核 查 IOAPIC 表,直接送到目标 vCPU/LAPIC。EOI :来宾写 LAPIC EOI → 内核里 处理,不再退出到 QEMU。无需 QEMU 参与 注入/EOI,延迟大幅降低 。KVM_IRQ_LINE 注入,但仍比全用户态快)

MSI‑X + irqfd(virtio/vhost/VFIO 常用,最快)

Raise :设备要发 MSI‑X,本质是一次写内存 到“APIC 目标地址 + 数据”。

仿真设备:QEMU可直接 kvm_irqchip_send_msi()(KVM_SIGNAL_MSI)。

vhost/VFIO :把每个中断向量绑定一个 irqfd (eventfd)。后端或硬件触发这个 eventfd。

Route/Deliver :KVM 内核根据 MSI 路由表 (GSI routing)直接把中断送达目标 vCPU 的 LAPIC,不退出 到 QEMU。

EOI :来宾 LAPIC EOI 在内核处理(若硬件有 APICv/PI,还能进一步减少退出)。消息信号 + in‑kernel + irqfd :常见最优路径 。

PCI 设备 PCI(Peripheral Component Interconnect) 是一套“主机 ↔ 外设”的标准总线与软件模型。它经历了演进:

PCI(并行) → PCI-X (并行/服务器) → PCIe(PCI Express,串行点到点) 。软件模型延续:都有配置空间(Configuration Space) 、BAR(Base Address Register) 、中断 、DMA 等概念;PCIe 只是物理与链路层 变了,并新增了很多能力(MSI-X、热插拔、错误报告、节能等)。

把主板想成一座城市:

CPU/Root Complex = 市政府PCIe Root Port / 交换机(Switch) = 城市立交各类设备(网卡、显卡、NVMe、FPGA…) = 公司大楼(Endpoint)

开机后,政府(Root Complex)把所有大楼“接上光纤”(链路训练 :速率/宽度握手),然后一栋栋盘点信息 (配置空间 ),分配门牌号 (BDF:Bus:Device.Function )和地盘 (BAR:一段可映射的地址 ),最后发工作许可(Bus Master )和电话分机(中断:MSI/MSI-X )。

设备要读写内存,就自己“DMA 去搬货”;

干完活,它打分机(MSI-X )通知 CPU;

CPU 的驱动接电话,继续分派任务。

这就是“PCI 设备”在机器里的日常。

典型的 PCIe 拓扑 :

1 2 3 CPU / Root Complex ├─ Root Port 0 ──[Switch]── NVMe(0000:65:00.0) └─ Root Port 1 ── GPU(0000:03:00.0)

每个功能都有个 BDF (域:总线:设备.功能),如 0000:65:00.0。

BDF/DBDF 编址 BDF/DBDF 编址格式 每个 PCI 设备通过一段 BB:DD.F 格式的数据编址来表示。BDF 是“枚举顺序 + 桥的划分”决定的,加/拔设备、换插槽、BIOS 升级、桥/Root Port 重新枚举,都可能改变 Bus 号甚至设备号。但同一机器同一拓扑下,BDF 通常稳定。

BDF :BB:DD.F

**Bus (BB,总线号)**:8 位 → 0..255(显示为 00..ff)

**Device (DD,设备号/插槽号)**:5 位 → 0..31(一个总线最多 32 个“设备号”)

**Function (F,功能号)**:3 位 → 0..7(同一设备号最多 8 个“功能”)

一个 PCI 设备(同一个 DD)最多有 8 个函数 (F=0..7),叫“多功能设备 ”:

典型例子:PCH(南桥)下面的 00:1f.0 LPC 、00:1f.2 SATA 、00:1f.3 SMBus … 它们共享同一个设备号 1f,功能号不同。

是否多功能由 Function 0 的 Header Type bit7 决定(1=多功能)。

驱动加载时按 Function 维度 匹配:每个 Function 都有独立的配置空间(Vendor/Device ID 也可能不同)。

DBDF :DDDD:BB:DD.F

**Domain/Segment (DDDD,域)**:16 位 → 0..FFFF(通常为 0000;多根 PCIe Root Complex、复杂 NUMA/加速卡/直通场景时可能 >0)

例如:

00:1f.2 = 总线 0、设备 31、功能 2;0000:65:00.0 = 域 0 的 65:00.0。

lspci 默认可能省略 0000:,用 -D 可强制显示域:lspci -D -s 65:00.0。其它常用命令如下:

总是显示域号(Domain):

看树:

看驱动/模块:

BDF 与机器拓扑 PCIe 是“树形 ”拓扑:Root Complex → Root Port →(可选)Switch → Endpoint。用 lspci -t(或 -tv)可以看到设备树,比如:

1 2 3 4 -+-[0000:65]-+-00.0 (Root Port) | \-00.1 (Root Port) \-[0000:66]-+-00.0 (Switch Upstream) \-[0000:67]-00.0 (你的网卡 67:00.0)

这里 67:00.067 就是被上面的桥划给它的子总线号 。

每一级“桥” (PCI-to-PCIe Bridge/Switch Port)在枚举时会配置三组“总线号寄存器”:

Primary Bus (桥自己所在的上游总线)Secondary Bus (桥下游第一个 子总线号)Subordinate Bus (桥下游最大 子总线号)

枚举时,固件/OS 会:

给桥分配 Secondary/Subordinate 的总线号区间 ;

在该区间内为下挂的设备分配 **Device(0..31)**,并探测其 Function ;

因此 Bus 号取决于桥的划分 ,Device/Function 再在该 Bus 内唯一。

DBDF 到文件系统的对应 在 sysfs 和 procfs 各有一套接口来映射 PCI 设备,它们不是同一个目录 。

BDF 与配置空间访问 访问配置空间时,必须用 Bus/Device/Function/Offset 这四元组索引到目标 Function:

也就是说,BDF 既是“名字”,也是访问坐标 。Domain/Segment 由 ACPI MCFG 指定不同段的 ECAM 基址,不参与 单个 PCIe 事务的 Requester ID(后者只有 Bus/Device/Function)。

配置空间 配置空间”(Configuration Space) 本质上就是“设备芯片内部的一堆寄存器” ,用于枚举/识别/配置 设备。操作系统通过“配置访问通道”把读/写请求 送到设备,设备把这些寄存器的内容返回。

配置空间结构 传统 PCI 的配置空间大小为 256 B ;而 PCIe 在次基础上有额外的 4 KiB 扩展配置空间 ,配置空间结构如下:

标准头(前 64B) 常见字段:

Vendor ID / Device ID:识别厂商与设备;Command(控制位):bit0 I/O Space、bit1 Memory Space、bit2 Bus Master(DMA 必须开)…Status:错误/能力支持等状态位;Class Code/Subclass/ProgIF:设备类别(网卡/存储/桥…);Header Type:0=端点,1=桥,2=CardBus;BAR0..BAR5 :最多 6 个基址寄存器(Endpoint 类型);Capabilities Pointer:指向“能力链表 ”(PM、MSI、MSI-X、PCIe Cap…)。

PCIe 扩展能力 在 4 KiB 的扩展能力空间 链表里(例如 AER、ACS、ARI、SR-IOV、ATS/PRI/PASID、L1 Substates…)。

配置空间查看 通过 lspci 命令 -s 参数指定 BDF 地址就可以查看对应设备的配置空间信息:

上述信息本质上是通过 sysfs 文件系统的 PCI 设备接口下的 config 文件查看的:

1 sudo cat /sys/bus/pci/devices/0000:65:00.0/config | xxd

另外 procfs 文件系统的 PCI 设备接口也可以查看 配置空间:

1 sudo cat /proc/bus/pci/65/00.0 | xxd

BAR 寄存器 BAR(Base Address Register)= 基址寄存器 。

设备用它来声明“我需要一扇对外的地址窗口 ”(可以是 I/O 空间或内存空间),操作系统据此在系统的地址空间中为它划一块不冲突的地址段 ,再把基址写回 BAR。之后:

CPU 访问“基址 + 偏移 ”就能访问到设备寄存器/缓冲区(MMIO 或 PIO );

设备内部的地址译码(decoder)看到这段地址,会把事务路由到对应的寄存器/存储阵列。

不同类型的 PCI 设备的 BAR 寄存器数量是不同的:

BAR 寄存器结构

I/O BAR(端口 I/O,主要在 x86)

bit0=1 表示这是 I/O 空间 (PIO)BAR;bits[31:2] 保存 端口基址 (低 2 位必须为 0,表示对齐);

Memory BAR(内存映射 I/O,MMIO)

查看 BAR 寄存器 通过 lspci 命令我们可以查看 BAR 寄存器的状态。

/sys/bus/pci/devices/0000:65:00.0/resource 是内核给这个 PCI 设备最终分配的所有“地址资源”的汇总表 。这个函数现在占了哪些地址段 ”一次性列出来:每行三列——起始地址、结束地址(包含)和标志位 。这些行主要来源于 BAR0..BAR5(以及可选的 Expansion ROM) 的分配结果;若该设备是桥 ,还会包含桥窗口(I/O window、non-prefetchable MEM window、prefetchable MEM window)等。

resource 的每一行格式为:

1 <start_phys_addr> <end_phys_addr> <flags>

resource0…resourceN :同目录下的 resource0、resource1… 是把每一行(尤其是 Memory BAR )单独“摊开”的节点:

Memory BAR 对应的 resourceX 可以 mmap (用户态调试常用),直接访问设备寄存器/窗口;I/O BAR(端口 I/O) 的那几行不可 mmap (它不是内存),要用 in/out 指令。

通信方式 PIO(Port-I/O,端口 I/O) PIO 是在 x86 体系特有的“I/O 端口地址空间 ”(和内存地址空间分离,最多 64K 端口)。设备采用 PIO 通信方式需要满足:

设备的 I/O BAR (BAR 的最低位为 1)指示它使用 I/O 空间。

将 Command.bit0 = 1(I/O Space Enable) 后,访问 I/O 端口才有效。

/proc/ioports ⇒ “I/O 端口地址空间”的占用清单 PIO 端口范围 ,通常是被驱动通过 request_region() 注册过的那部分(比如 0x3f8-0x3ff : serial、0xcf8-0xcff : PCI conf1)。没被注册的端口段可能不会显示。

Port-mapped I/O(x86 的“端口 I/O”)没有“物理内存地址” 这个概念,只有I/O 端口号 (port number,x86 上是 0–0xFFFF)。访问用 in/out 指令或 /dev/port,不能 mmap 到用户虚拟地址,也不会出现在 /proc/pagemap 里。

CPU 用 in/out 指令访问这些端口。

x86 的 IN/OUT 指令族采用 16 位端口号(I/O 地址空间 0..65535),数据宽度只有 8/16/32 位 (没有 64 位)。

inb/outb ⇒ 8 位(AL)inw/outw ⇒ 16 位(AX)inl/outl ⇒ 32 位(EAX,在 x86-64 也用 32 位形式)

指令只允许“累加器”作为数据寄存器:读入到 AL/AX/EAX,或从 AL/AX/EAX 写出;端口在 DX 或 8 位立即数。

端口号在 DX:in al, dx / in ax, dx / in eax, dx;out dx, al/ax/eax

端口号是 8 位立即数(零扩展成 16 位):in al, imm8 / out imm8, al(常用于固定小端口,如 0x60)

sys/io.h 提供相关函数封装:inb/inw/inl/outb/outw/outl(这些就是对 IN/OUT 的内联汇编封装)。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 #include <sys/io.h> unsigned char inb (unsigned short port) ;unsigned char inb_p (unsigned short port) ;unsigned short inw (unsigned short port) ;unsigned short inw_p (unsigned short port) ;unsigned int inl (unsigned short port) ;unsigned int inl_p (unsigned short port) ;void outb (unsigned char value, unsigned short port) ;void outb_p (unsigned char value, unsigned short port) ;void outw (unsigned short value, unsigned short port) ;void outw_p (unsigned short value, unsigned short port) ;void outl (unsigned int value, unsigned short port) ;void outl_p (unsigned int value, unsigned short port) ;void insb (unsigned short port, void *addr, unsigned long count) ;void insw (unsigned short port, void *addr, unsigned long count) ;void insl (unsigned short port, void *addr, unsigned long count) ;void outsb (unsigned short port, const void *addr, unsigned long count) ;void outsw (unsigned short port, const void *addr, unsigned long count) ;void outsl (unsigned short port, const void *addr, unsigned long count) ;

在 Linux 下,用户态线程默认不能 执行 inb/outb/inw/outw/inl/outl 这类 I/O 指令。原因是 CPU 会检查调用线程有没有 I/O 端口访问权限;没有的话直接触发保护异常(程序崩掉)。

下面两个 api 都可以获取 I/O 访问权限,但是前提都需要 CAP_SYS_RAWIO 能力,即允许执行 ioperm/iopl 等原始 I/O 操作。

ioperm(base, len, 1)[base, base+len) 这段端口范围,因此你就能对这段端口执行 in/out。需要 CAP_SYS_RAWIO 能力或 root。ioperm 是按端口范围细粒度授权 的,现代内核支持到 65536 个端口。

iopl(3)对所有端口 都有访问权。也需要 CAP_SYS_RAWIO。官方文档标注它已不推荐 ,比 ioperm 慢,主要为了老式 X 服务器遗留场景;而且在新内核(≥3.7)上它的继承行为与早期不同。

PIO 读写模板:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 #define _GNU_SOURCE #include <errno.h> #include <inttypes.h> #include <stdbool.h> #include <stdint.h> #include <stdio.h> #include <stdlib.h> #include <string.h> #include <sys/io.h> #include <unistd.h> #define IORESOURCE_IO 0x00000100ULL typedef struct { uint16_t base; uint32_t size; uint16_t grant_base; uint32_t grant_len; bool have_ioperm; bool have_iopl; bool inited; } pio_ctx_t ; static pio_ctx_t g_pio = {0 };static int parse_io_bar (const char *bdf_or_path, int bar_idx, uint16_t *out_base, uint32_t *out_size) { char path[256 ]; if (strchr (bdf_or_path, '/' )) { snprintf (path, sizeof (path), "%s" , bdf_or_path); } else { snprintf (path, sizeof (path), "/sys/bus/pci/devices/%s/resource" , bdf_or_path); } FILE *fp = fopen(path, "r" ); if (!fp) return -1 ; int idx = 0 , chosen = -1 ; char line[256 ]; while (fgets(line, sizeof (line), fp)) { unsigned long long start = 0 , end = 0 , flags = 0 ; if (sscanf (line, "%llx %llx %llx" , &start, &end, &flags) != 3 ) { idx++; continue ; } if (bar_idx >= 0 ) { if (idx == bar_idx) { if (!(flags & IORESOURCE_IO)) { fclose(fp); errno = EINVAL; return -1 ; } if (end < start || start > 0xFFFF ULL) { fclose(fp); errno = ERANGE; return -1 ; } *out_base = (uint16_t )start; *out_size = (uint32_t )(end - start + 1 ); chosen = idx; break ; } } else { if (idx <= 5 && (flags & IORESOURCE_IO)) { if (end < start || start > 0xFFFF ULL) { fclose(fp); errno = ERANGE; return -1 ; } *out_base = (uint16_t )start; *out_size = (uint32_t )(end - start + 1 ); chosen = idx; break ; } } idx++; } fclose(fp); if (chosen < 0 ) { errno = ENOENT; return -1 ; } return 0 ; } static int acquire_io_priv (uint16_t base, uint32_t size, uint16_t *grant_base, uint32_t *grant_len, bool *have_ioperm, bool *have_iopl) { uint32_t len = size; if ((unsigned )base + len > 0x10000 u) len = 0x10000 u - base; if (len == 0 ) len = 1 ; if (ioperm(base, len, 1 ) == 0 ) { *grant_base = base; *grant_len = len; *have_ioperm = true ; *have_iopl = false ; return 0 ; } if (iopl(3 ) == 0 ) { *grant_base = 0 ; *grant_len = 0 ; *have_ioperm = false ; *have_iopl = true ; return 0 ; } return -1 ; } int pio_init (const char *bdf_or_path, int bar_idx) { if (g_pio.inited) { errno = EALREADY; return -1 ; } uint16_t base = 0 ; uint32_t size = 0 ; if (parse_io_bar(bdf_or_path, bar_idx, &base, &size) != 0 ) return -1 ; uint16_t gbase = 0 ; uint32_t glen = 0 ; bool have_perm = false , have_iopl = false ; if (acquire_io_priv(base, size, &gbase, &glen, &have_perm, &have_iopl) != 0 ) return -1 ; g_pio.base = base; g_pio.size = size; g_pio.grant_base = gbase; g_pio.grant_len = glen; g_pio.have_ioperm= have_perm; g_pio.have_iopl = have_iopl; g_pio.inited = true ; return 0 ; } void pio_fini (void ) { if (!g_pio.inited) return ; if (g_pio.have_ioperm) (void )ioperm(g_pio.grant_base, g_pio.grant_len, 0 ); if (g_pio.have_iopl) (void )iopl(0 ); memset (&g_pio, 0 , sizeof (g_pio)); } uint16_t pio_base (void ) { return g_pio.base; }uint32_t pio_size (void ) { return g_pio.size; }static inline int pio_port (uint32_t off, int width, uint16_t *port_out) { if (!g_pio.inited) { errno = EPERM; return -1 ; } if ((uint64_t )off + (uint64_t )width > g_pio.size) { errno = ERANGE; return -1 ; } uint32_t p = (uint32_t )g_pio.base + off; if (p > 0xFFFF u) { errno = ERANGE; return -1 ; } *port_out = (uint16_t )p; return 0 ; } uint8_t pio_read8 (uint32_t off) { uint16_t p; if (pio_port(off,1 ,&p)) return 0 ; return inb(p); }uint16_t pio_read16 (uint32_t off) { uint16_t p; if (pio_port(off,2 ,&p)) return 0 ; return inw(p); }uint32_t pio_read32 (uint32_t off) { uint16_t p; if (pio_port(off,4 ,&p)) return 0 ; return inl(p); }void pio_write8 (uint32_t off, uint8_t v) { uint16_t p; if (pio_port(off,1 ,&p)) return ; outb(v,p); }void pio_write16 (uint32_t off, uint16_t v) { uint16_t p; if (pio_port(off,2 ,&p)) return ; outw(v,p); }void pio_write32 (uint32_t off, uint32_t v) { uint16_t p; if (pio_port(off,4 ,&p)) return ; outl(v,p); }

使用示例:

1 2 3 4 5 6 7 8 9 10 11 int main () { if (pio_init("0000:00:04.0" , -1 ) != 0 ) { perror("pio_init" ); return 1 ; } printf ("PIO base=0x%04x size=0x%x\n" , pio_base(), pio_size()); uint32_t v = pio_read32(0x64 ); printf ("R32 @ +0x64 = 0x%08x\n" , v); pio_write32(0x64 , v | 1 ); pio_fini(); return 0 ; }

MMIO(Memory-Mapped I/O,内存映射 I/O) MMIO 指的是把设备的一段寄存器/门铃窗口“映射”到物理地址空间 (由 BAR 决定)。CPU 用普通的内存读写 指令访问这些地址,就等价于在读写设备寄存器。

设备在配置空间里有 BAR0..BAR5 。固件/OS 为 Memory BAR 分配一段对齐的物理地址,并把这个地址写回 BAR。

/proc/iomem ⇒ “物理内存地址空间”的全局地图 MMIO 区 (设备的 memory BAR)、以及 System RAM、ACPI/固件、ROM、内核代码数据、主桥下行 window 等等。也就是:不止 MMIO,但所有 MMIO 都会在这里出现 。

对 设备 MMIO 的用户态映射 (通过 /sys/.../resourceN 或 /dev/mem + remap_pfn_range 建出来的 VM_IO | VM_PFNMAP VMA),/proc/self/pagemap 不会 给出有效 PFN,很多内核版本直接把 PFN 置 0(或把 present 位清掉),因此你对 g_mmio.bar 调 virt_to_phys() 会得到 0 → 打印成 (nil)。而匿名页是普通 RAM,所以能拿到 0x2e08000 这种正常的物理地址。

换句话说:pagemap 只适合“内存页(RAM)” ,不适合设备 I/O 映射 。MMIO 的“物理地址”应当由映射来源 来确定,而不是再去反查 pagemap。

MMIO 读写模板:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 192 193 #define _GNU_SOURCE #include <errno.h> #include <fcntl.h> #include <inttypes.h> #include <stdbool.h> #include <stddef.h> #include <stdint.h> #include <stdio.h> #include <stdlib.h> #include <limits.h> #include <string.h> #include <sys/mman.h> #include <sys/stat.h> #include <sys/types.h> #include <unistd.h> #define IORESOURCE_MEM 0x00000200ULL typedef struct { volatile uint8_t *bar; size_t size; size_t map_len; int fd; int res_idx; uint64_t phys_start; uint64_t phys_end; unsigned long long res_flags; bool inited; } mmio_ctx_t ; static mmio_ctx_t g_mmio = {0 };static int build_paths (const char *bdf_or_path, char *resource_txt, size_t txt_sz, char *dev_dir, size_t dir_sz) { if (!bdf_or_path || !*bdf_or_path) { errno = EINVAL; return -1 ; } if (strchr (bdf_or_path, '/' )) { snprintf (resource_txt, txt_sz, "%s" , bdf_or_path); snprintf (dev_dir, dir_sz, "%s" , bdf_or_path); char *slash = strrchr (dev_dir, '/' ); if (!slash) { errno = EINVAL; return -1 ; } *slash = '\0' ; if (strstr (resource_txt, "/resource" ) && resource_txt[strlen (resource_txt)-1 ] >= '0' && resource_txt[strlen (resource_txt)-1 ] <= '9' ) { snprintf (resource_txt, txt_sz, "%s/resource" , dev_dir); } } else { snprintf (resource_txt, txt_sz, "/sys/bus/pci/devices/%s/resource" , bdf_or_path); snprintf (dev_dir, dir_sz, "/sys/bus/pci/devices/%s" , bdf_or_path); } return 0 ; } static int parse_mem_bar (const char *resource_txt, int bar_idx, unsigned long long *start, unsigned long long *end, unsigned long long *flags, int *picked_idx) { FILE *fp = fopen(resource_txt, "r" ); if (!fp) return -1 ; int idx = 0 , sel = -1 ; char line[256 ]; while (fgets(line, sizeof (line), fp)) { unsigned long long s=0 , e=0 , f=0 ; if (sscanf (line, "%llx %llx %llx" , &s, &e, &f) != 3 ) { idx++; continue ; } if (bar_idx >= 0 ) { if (idx == bar_idx) { if (!(f & IORESOURCE_MEM) || e < s) { fclose(fp); errno = EINVAL; return -1 ; } sel = idx; if (start) *start = s; if (end) *end = e; if (flags) *flags = f; break ; } } else { if (idx <= 5 && (f & IORESOURCE_MEM)) { if (e < s) { fclose(fp); errno = ERANGE; return -1 ; } sel = idx; if (start) *start = s; if (end) *end = e; if (flags) *flags = f; break ; } } idx++; } fclose(fp); if (sel < 0 ) { errno = ENOENT; return -1 ; } if (picked_idx) *picked_idx = sel; return 0 ; } int mmio_init (const char *bdf_or_path, int bar_idx) { if (g_mmio.inited) { errno = EALREADY; return -1 ; } char resource_txt[PATH_MAX]; char dev_dir[PATH_MAX]; if (build_paths(bdf_or_path, resource_txt, sizeof (resource_txt), dev_dir, sizeof (dev_dir)) != 0 ) return -1 ; unsigned long long start=0 , end=0 , flags=0 ; int res_idx = -1 ; if (parse_mem_bar(resource_txt, bar_idx, &start, &end, &flags, &res_idx) != 0 ) return -1 ; size_t size = (size_t )((end - start) + 1ULL ); size_t pg = (size_t )sysconf(_SC_PAGESIZE); size_t map_len = (size + pg - 1 ) & ~(pg - 1 ); char res_path[PATH_MAX]; snprintf (res_path, sizeof (res_path), "%s/resource%d" , dev_dir, res_idx); int fd = open(res_path, O_RDWR | O_SYNC); if (fd < 0 ) return -1 ; void *map = mmap(NULL , map_len, PROT_READ | PROT_WRITE, MAP_SHARED, fd, 0 ); if (map == MAP_FAILED) { int sv = errno; close(fd); errno = sv; return -1 ; } g_mmio.bar = (volatile uint8_t *)map ; g_mmio.size = size; g_mmio.map_len = map_len; g_mmio.fd = fd; g_mmio.res_idx = res_idx; g_mmio.phys_start = (uint64_t )start; g_mmio.phys_end = (uint64_t )end; g_mmio.res_flags = flags; g_mmio.inited = true ; return 0 ; } void mmio_fini (void ) { if (!g_mmio.inited) return ; if (g_mmio.bar) munmap((void *)g_mmio.bar, g_mmio.map_len); if (g_mmio.fd >= 0 ) close(g_mmio.fd); memset (&g_mmio, 0 , sizeof (g_mmio)); } volatile void *mmio_base (void ) { return g_mmio.bar; }size_t mmio_size (void ) { return g_mmio.size; }int mmio_bar_index (void ) { return g_mmio.res_idx; }uint64_t mmio_phys_base (void ) { return g_mmio.phys_start; }uint64_t mmio_phys_limit (void ) { return g_mmio.phys_end; } uint64_t mmio_offset_to_phys (size_t off) { if (!g_mmio.inited) { errno = EPERM; return 0 ; } if (off >= g_mmio.size) { errno = ERANGE; return 0 ; } return g_mmio.phys_start + (uint64_t )off; } uint64_t mmio_virt_to_phys (const void *p) { if (!g_mmio.inited || !p) { errno = EPERM; return 0 ; } uintptr_t base = (uintptr_t )g_mmio.bar; uintptr_t addr = (uintptr_t )p; if (addr < base || addr >= base + g_mmio.size) { errno = EINVAL; return 0 ; } size_t off = (size_t )(addr - base); return g_mmio.phys_start + (uint64_t )off; } static inline int chk (size_t off, size_t width) { if (!g_mmio.inited) { errno = EPERM; return -1 ; } if (off + width > g_mmio.size) { errno = ERANGE; return -1 ; } return 0 ; } uint8_t mmio_read8 (size_t off) { if (chk(off,1 )) return 0 ; return *(volatile uint8_t *)(g_mmio.bar + off); }uint16_t mmio_read16 (size_t off) { if (chk(off,2 )) return 0 ; return *(volatile uint16_t *)(g_mmio.bar + off); }uint32_t mmio_read32 (size_t off) { if (chk(off,4 )) return 0 ; return *(volatile uint32_t *)(g_mmio.bar + off); }uint64_t mmio_read64 (size_t off) { if (chk(off,8 )) return 0 ; return *(volatile uint64_t *)(g_mmio.bar + off); }void mmio_write8 (size_t off, uint8_t v) { if (chk(off,1 )) return ; *(volatile uint8_t *)(g_mmio.bar + off) = v; }void mmio_write16 (size_t off, uint16_t v) { if (chk(off,2 )) return ; *(volatile uint16_t *)(g_mmio.bar + off) = v; }void mmio_write32 (size_t off, uint32_t v) { if (chk(off,4 )) return ; *(volatile uint32_t *)(g_mmio.bar + off) = v; }void mmio_write64 (size_t off, uint64_t v) { if (chk(off,8 )) return ; *(volatile uint64_t *)(g_mmio.bar + off) = v; }volatile void *mmio_ptr (size_t off) { if (chk(off,1 )) return NULL ; return (volatile void *)(g_mmio.bar + off); }

数据结构 1 2 3 4 5 6 7 8 9 10 11 12 13 14 typedef struct { volatile uint8_t *bar; size_t size; size_t map_len; int fd; int res_idx; uint64_t phys_start; uint64_t phys_end; unsigned long long res_flags; bool inited; } mmio_ctx_t ;

说明 :g_mmio 为内部全局上下文,API 都在此单实例上操作。

初始化与释放 int mmio_init(const char *bdf_or_path, int bar_idx);void mmio_fini(void);

功能 :解除映射、关闭 fd,清空 g_mmio。注意 :调用后,任何读写/查询接口都不再有效。

查询接口 1 2 3 4 5 6 volatile void *mmio_base (void ) ; size_t mmio_size (void ) ; int mmio_bar_index (void ) ; uint64_t mmio_phys_base (void ) ; uint64_t mmio_phys_limit (void ) ;

提示 :mmio_base() 返回的是进程虚拟地址 ;mmio_phys_base() 返回设备物理地址 。

地址换算 uint64_t mmio_offset_to_phys(size_t off);

功能 :把映射内偏移 换算为设备物理地址 。公式 :phys = phys_start + off边界 :off < g_mmio.size;否则置 errno=ERANGE 并返回 0。

uint64_t mmio_virt_to_phys(const void *p);

功能 :把映射内某虚拟指针 换算为设备物理地址 。公式 :phys = phys_start + ((uintptr_t)p - (uintptr_t)bar)边界 :p 必须位于 [bar, bar + size);否则置 errno=EINVAL 并返回 0。

注意 :这些 “物理地址” 指的是 CPU 物理地址空间中的 MMIO 区间 (BAR),不是 设备 DMA 侧地址。若系统启用 IOMMU,设备做 DMA 看到的是设备地址 ,与此不同。

寄存器访问 1 2 3 4 5 6 7 8 9 10 11 uint8_t mmio_read8 (size_t off) ;uint16_t mmio_read16 (size_t off) ;uint32_t mmio_read32 (size_t off) ;uint64_t mmio_read64 (size_t off) ;void mmio_write8 (size_t off, uint8_t v) ;void mmio_write16 (size_t off, uint16_t v) ;void mmio_write32 (size_t off, uint32_t v) ;void mmio_write64 (size_t off, uint64_t v) ;volatile void *mmio_ptr (size_t off) ;

入参 :off 是寄存器偏移 (相对于 BAR 起点),要求 off + width <= size。

返回/行为 :

读函数在越界时返回 0 并设置 errno=ERANGE。

写函数在越界时不执行写入 。

mmio_ptr(off) 返回 bar + off 的直接指针 (volatile),越界返回 NULL。

端序 :PCI/PC 常见为小端 寄存器布局;上面函数按本机字节序单纯取/存(在小端主机上与寄存器端序一致)。如目标为大端或寄存器定义为特定端序,需在调用处处理端序。

对齐 :建议按天然宽度对齐访问(例如 32 位寄存器用 mmio_read32/write32 且 off%4==0),避免未对齐访问带来的架构差异。

返回值与错误处理

使用示例:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 #include <stdio.h> #include <inttypes.h> int main () { if (mmio_init("0000:00:04.0" , 0 ) != 0 ) { perror("mmio_init" ); return 1 ; } printf ("VA base = %p\n" , mmio_base()); printf ("PA base = 0x%016" PRIx64 "\n" , mmio_phys_base()); printf ("PA end = 0x%016" PRIx64 " (size=%zu)\n" , mmio_phys_limit(), mmio_size()); size_t off = 0x100 ; uint32_t v = mmio_read32(off); printf ("READ32[0x%zx] = 0x%08x\n" , off, v); mmio_write32(off, v | 0x1 ); printf ("PA(off=0x%zx) = 0x%016" PRIx64 "\n" , off, mmio_offset_to_phys(off)); volatile void *p = mmio_ptr(0x200 ); printf ("PA(ptr=%p) = 0x%016" PRIx64 "\n" , (void *)p, mmio_virt_to_phys((void *)p)); mmio_fini(); return 0 ; }

QEMU Object Model QEMU Object Model(QOM)就是 QEMU 在 C 语言 里自建的一套“面向对象”系统,用来统一建模和管理模拟中的一切东西(CPU、总线、设备、内存、机器等)。它提供类型系统、继承/接口、对象树、属性、以及设备生命周期(realize/unrealize)等机制,让设备能被配置、热插拔、迁移,并能被 QMP/HMP 进行自省(introspection)。

Type :概念上的“类定义”。在源码里先写一个 TypeInfoTypeImpl**(内部表示,放到全局哈希表里)。Class :某个类型的类对象 (保存“虚函数表”等静态行为),类型初始化后得到一个 ObjectClassObject :某个类型的实例对象 ,动态分配的 **Object**(或其派生,比如 DeviceState 内含的 Object 头)。Property :对象/类对外暴露的属性访问器 (getter/setter 或指向子对象/链接),用于命令行与 QMP 自省。

classDiagram

direction LR

class TypeInfo {

+const char* name

+const char* parent

+size_t instance_size

+size_t instance_align

+void (*instance_init)(Object*)

+void (*instance_post_init)(Object*)

+void (*instance_finalize)(Object*)

+bool abstract

+size_t class_size

+void (*class_init)(ObjectClass*, const void*)

+void (*class_base_init)(ObjectClass*, const void*)

+const void* class_data

+InterfaceInfo[] interfaces

}

class TypeImpl {

+const char* name

+size_t class_size

+size_t instance_size

+size_t instance_align

+void (*class_init)(ObjectClass*, const void*)

+void (*class_base_init)(ObjectClass*, const void*)

+const void* class_data

+void (*instance_init)(Object*)

+void (*instance_post_init)(Object*)

+void (*instance_finalize)(Object*)

+bool abstract

+const char* parent

+TypeImpl* parent_type

+ObjectClass* class %% 单例 class 对象

+int num_interfaces

+InterfaceImpl interfaces[*]

}

class ObjectClass {

+Type type %% 指回本类的 TypeImpl

+GSList* interfaces %% InterfaceClass 列表(按类挂载)

+const char* object_cast_cache[4]

+const char* class_cast_cache[4]

+ObjectUnparent* unparent

+GHashTable* properties

}

class Object {

+ObjectClass* class %% 指向所属类

+ObjectFree* free

+GHashTable* properties

+uint32_t ref

+Object* parent

}

class InterfaceInfo {

+const char* type %% 接口类型名(注册时声明)

}

class InterfaceImpl {

+const char* typename %% 运行时保存的接口名

}

class InterfaceClass {

<>

+ObjectClass parent_class

+Type interface_type %% 指向接口自身的 TypeImpl

}

%% 关系

TypeInfo --> TypeImpl : type_register_static()

TypeImpl --> TypeImpl : parent_type

TypeImpl *-- ObjectClass : class (singleton)

Object --> ObjectClass : class

ObjectClass --> TypeImpl : type

TypeInfo --> InterfaceInfo : interfaces

TypeImpl --> InterfaceImpl : interfaces

InterfaceClass --|> ObjectClass : subclass

ObjectClass o-- "0..*" InterfaceClass : interfaces (per-class)

InterfaceClass --> TypeImpl : interface_type

QOM整个运作包括3个部分,即类型的注册、类型的初始化以及对象的初始化。

类型的注册 TypeInfo 这一结构体用来定义一个「类」的基本属性,该结构体定义于 include/qom/object.h 当中:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 struct TypeInfo { const char *name; const char *parent; size_t instance_size; void (*instance_init)(Object *obj); void (*instance_post_init)(Object *obj); void (*instance_finalize)(Object *obj); bool abstract; size_t class_size; void (*class_init)(ObjectClass *klass, void *data); void (*class_base_init)(ObjectClass *klass, void *data); void *class_data; InterfaceInfo *interfaces; };

以 hw/misc/edu.c 文件为例,当我们在 Qemu 中要定义一个「类」的时候,我们实际上需要定义一个 TypeInfo 类型的变量。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 static void pci_edu_register_types (void ) { static InterfaceInfo interfaces[] = { { INTERFACE_CONVENTIONAL_PCI_DEVICE }, { }, }; static const TypeInfo edu_info = { .name = TYPE_PCI_EDU_DEVICE, .parent = TYPE_PCI_DEVICE, .instance_size = sizeof (EduState), .instance_init = edu_instance_init, .class_init = edu_class_init, .interfaces = interfaces, }; type_register_static(&edu_info); } type_init(pci_edu_register_types)

可以看到各个 QOM 类型最终通过函数 register_module_init 注册到了系统,其中 function 是每个类型都需要实现的初始化函数,type 表示是 MODULE_INIT_QOM 。

这里的 constructor 是编译器属性,编译器会把带有这个属性的函数 do_qemu_init_ ##function 放到特殊的段中,带有这个属性的函数会早于 main 函数执行,也就是说所有的 QOM 类型注册在 main 执行之前就已经执行了。

1 2 3 4 5 6 7 #define module_init(function, type) \ static void __attribute__((constructor)) do_qemu_init_ ## function(void) \ { \ register_module_init(function, type); \ } #define type_init(function) module_init(function, MODULE_INIT_QOM)

register_module_init 及相关函数代码如下:

1 2 3 4 5 6 7 8 9 10 11 12 13 void register_module_init (void (*fn)(void ), module_init_type type) { ModuleEntry *e; ModuleTypeList *l; e = g_malloc0(sizeof (*e)); e->init = fn; e->type = type; l = find_type(type); QTAILQ_INSERT_TAIL(l, e, node); }

register_module_init 函数以类型的初始化函数以及所属类型(对 QOM 类型来说是 MODULE_INIT_QOM )构建出一个 ModuleEntry,然后插入到对应 module 所属的链表中,所有 module 的链表存放在一个 init_type_list 数组中。

进入 main 函数后不久就以 MODULE_INIT_QOM 为参数调用了函数 module_call_init。

1 2 3 int main (int argc, char **argv, char **envp) qemu_init (argc, argv, envp) ; module_call_init(MODULE_INIT_QOM);

这个函数执行了 init_type_list[MODULE_INIT_QOM] 链表上每一个 ModuleEntry 的 init 函数。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 void module_call_init (module_init_type type) { ModuleTypeList *l; ModuleEntry *e; if (modules_init_done[type]) { return ; } l = find_type(type); QTAILQ_FOREACH(e, l, node) { e->init(); } modules_init_done[type] = true ; }

以 edu 设备为例,该类型的 init 函数是 pci_edu_register_types,该函数唯一的工作是构造了一个 TypeInfo 类型的 edu_info,并将其作为参数调用 type_register_static,type_register_static 调用 type_register,最终到达了 type_register_internal,核心工作在这一函数中进行。

type_register_internal 函数很简单,type_new 函数首先通过一个 TypeInfo 结构构造出一个 TypeImpl,type_table_add 则将这个 TypeImpl 加入到一个哈希表中。这个哈希表的 key 是 TypeImpl 的名字,value 为 TypeImpl 本身的值。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 static TypeImpl *type_new (const TypeInfo *info) { TypeImpl *ti = g_malloc0(sizeof (*ti)); int i; g_assert(info->name != NULL ); if (type_table_lookup(info->name) != NULL ) { fprintf (stderr , "Registering `%s' which already exists\n" , info->name); abort (); } ti->name = g_strdup(info->name); ti->parent = g_strdup(info->parent); ti->class_size = info->class_size; ti->instance_size = info->instance_size; ti->class_init = info->class_init; ti->class_base_init = info->class_base_init; ti->class_data = info->class_data; ti->instance_init = info->instance_init; ti->instance_post_init = info->instance_post_init; ti->instance_finalize = info->instance_finalize; ti->abstract = info->abstract; for (i = 0 ; info->interfaces && info->interfaces[i].type; i++) { ti->interfaces[i].typename = g_strdup(info->interfaces[i].type); } ti->num_interfaces = i; return ti; } static GHashTable *type_table_get (void ) { static GHashTable *type_table; if (type_table == NULL ) { type_table = g_hash_table_new(g_str_hash, g_str_equal); } return type_table; } static void type_table_add (TypeImpl *ti) { assert(!enumerating_types); g_hash_table_insert(type_table_get(), (void *)ti->name, ti); } static TypeImpl *type_register_internal (const TypeInfo *info) { TypeImpl *ti; ti = type_new(info); type_table_add(ti); return ti; }

TypeImpl 中存放了类型的所有信息,其定义如下。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 struct TypeImpl { const char *name; size_t class_size; size_t instance_size; void (*class_init)(ObjectClass *klass, void *data); void (*class_base_init)(ObjectClass *klass, void *data); void *class_data; void (*instance_init)(Object *obj); void (*instance_post_init)(Object *obj); void (*instance_finalize)(Object *obj); bool abstract; const char *parent; TypeImpl *parent_type; ObjectClass *class ; int num_interfaces; InterfaceImpl interfaces[MAX_INTERFACES]; };

类型的初始化 类的初始化是通过 type_initialize 函数完成的,这个函数并不长,函数的输入是表示类型信息的 TypeImpl 类型 ti。函数首先判断了 ti->class 是否存在,如果不为空就表示这个类型已经初始化过了,直接返回。

1 2 3 if (ti->class) { return ; }

后面主要做了三件事:

第一件事是设置相关的 filed,比如 class_size 和 instance_size,使用 ti->class_size 分配一个 ObjectClass。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 ti->class_size = type_class_get_size(ti); ti->instance_size = type_object_get_size(ti); if (ti->instance_size == 0 ) { ti->abstract = true ; } if (type_is_ancestor(ti, type_interface)) { assert(ti->instance_size == 0 ); assert(ti->abstract); assert(!ti->instance_init); assert(!ti->instance_post_init); assert(!ti->instance_finalize); assert(!ti->num_interfaces); } ti->class =

第二件事就是初始化所有父类类型,不仅包括实际的类型,也包括接口这种抽象类型。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 parent = type_get_parent(ti); if (parent) { type_initialize(parent); GSList *e; int i; g_assert(parent->class_size <= ti->class_size); g_assert(parent->instance_size <= ti->instance_size); memcpy (ti->class, parent->class, parent->class_size); ti->class ->NULL ; ti->class -> g_str_hash, g_str_equal, NULL , object_property_free); for (e = parent->class->interfaces; e; e = e->next) { InterfaceClass *iface = e->data; ObjectClass *klass = OBJECT_CLASS(iface); type_initialize_interface(ti, iface->interface_type, klass->type); } for (i = 0 ; i < ti->num_interfaces; i++) { TypeImpl *t = type_get_by_name(ti->interfaces[i].typename); if (!t) { error_report("missing interface '%s' for object '%s'" , ti->interfaces[i].typename, parent->name); abort (); } for (e = ti->class->interfaces; e; e = e->next) { TypeImpl *target_type = OBJECT_CLASS(e->data)->type; if (type_is_ancestor(target_type, t)) { break ; } } if (e) { continue ; } type_initialize_interface(ti, t, t); } } else { ti->class->properties = g_hash_table_new_full( g_str_hash, g_str_equal, NULL , object_property_free); } ti->class ->

第三件事就是依次调用所有父类的 class_base_init 以及自己的 class_init,这也和 C++ 很类似,在初始化一个对象的时候会依次调用所有父类的构造函数。这里是调用了父类型的 class_base_init 函数。

按祖先链自下而上依次调用各祖先的 class_base_init;

只调用本类的 class_init(祖先的 class_init 在祖先初始化时已经调用过了)。

1 2 3 4 5 6 7 8 9 10 while (parent) { if (parent->class_base_init) { parent->class_base_init(ti->class, ti->class_data); } parent = type_get_parent(parent); } if (ti->class_init) { ti->class_init(ti->class, ti->class_data); }

实际上 type_initialize 函数可以在很多地方调用,不过,只有在第一次调用的时候会进行初始化,之后的调用会由于 ti->class 不为空而直接返回。

下面以其中一条路径来看 type_initialize 函数的调用过程。假设在启动 QEMU 虚拟机的时候不指定 machine 参数,那 QEMU 会在 main 函数中调用 select_machine,进而由 find_default_machine 函数来找默认的 machine 类型。在那个函数之前,会调用 object_class_get_list 来得到所有 TYPE_MACHINE 类型组成的链表。

1 2 3 4 int main (int argc, char **argv, char **envp) > machine_class = select_machine(); > GSList *machines = object_class_get_list(TYPE_MACHINE, false ); > MachineClass *machine_class = find_default_machine(machines);

object_class_get_list 会调用 object_class_foreach,后者会对 type_table 中所有类型调用 object_class_foreach_tramp 函数,在该函数中会调用 type_initialize 函数。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 GSList *object_class_get_list (const char *implements_type, bool include_abstract) { GSList *list = NULL ; object_class_foreach(object_class_get_list_tramp, implements_type, include_abstract, &list ); return list ; } void object_class_foreach (void (*fn)(ObjectClass *klass, void *opaque), const char *implements_type, bool include_abstract, void *opaque) { OCFData data = { fn, implements_type, include_abstract, opaque }; enumerating_types = true ; g_hash_table_foreach(type_table_get(), object_class_foreach_tramp, &data); enumerating_types = false ; } static void object_class_foreach_tramp (gpointer key, gpointer value, gpointer opaque) { OCFData *data = opaque; TypeImpl *type = value; ObjectClass *k; type_initialize(type); k = type->class; if (!data->include_abstract && type->abstract) { return ; } if (data->implements_type && !object_class_dynamic_cast(k, data->implements_type)) { return ; } data->fn(k, data->opaque); }

类型的层次结构 在 edu 这个设备的类型信息里(edu_info),有个 parent 字段,写着它的父类型是谁。

对 edu 来说,父类型是 TYPE_PCI_DEVICE。而 TYPE_PCI_DEVICE 的父类型是 TYPE_DEVICE,再往上是 TYPE_OBJECT。换句话说,类型继承链是:TYPE_OBJECT → TYPE_DEVICE → TYPE_PCI_DEVICE → edu。

QEMU 的所有类型都挂在这棵以 TYPE_OBJECT 为根的树上。

初始化类型时(type_initialize),QEMU 会给“类对象”(class)分配内存,这个“类对象”并不是 C++ 的 class,但作用很像:它保存了某个类型的“方法表/元数据”(回调函数、标识字段等)。

1 ti->class =

class_size 决定了这个“类对象”到底长啥样(也就是用哪种结构体)。如果当前类型没自己指定 class_size,就沿用父类型的 class_size。

在 edu 设备的类型信息 edu_info 结构中有一个 parent 成员,这就指定了 edu_info 的父类型的名称,通过分析源码可知继承关系为 TYPE_PCI_DEVICE->TYPE_DEVICE->TYPE_OBJECT。总体上,QEMU 使用的类型一起构成了以 TYPE_OBJECT 为根的树。

1 2 3 4 5 6 7 8 static const TypeInfo edu_info = { .name = TYPE_PCI_EDU_DEVICE, .parent = TYPE_PCI_DEVICE, .instance_size = sizeof(EduState), .instance_init = edu_instance_init, .class_init = edu_class_init, .interfaces = interfaces, };

edu 类型没有定义自己的 class_size,所以直接继承父类型 TYPE_PCI_DEVICE 的 class_size。父类型的类结构体就是 PCIDeviceClass,因此 edu 的类对象类型也就是 PCIDeviceClass(里面包含 realize/exit/config_read/config_write 等回调,以及 vendor/device/class 等标识字段)。

在类型的初始化函数 type_initialize 中会调用 ti->class=g_malloc0(ti->class_size) 语句来分配类型的 class 结构,这个结构实际上代表了类型的信息。类似于 C++ 定义的一个类,从前面的分析看到 ti->class_size 为 TypeImpl 中的值,如果类型本身没有定义就会使用父类型的 class_size 进行初始化。edu 设备中的类型本身没有定义,所以它的 class_size 为 TYPE_PCI_DEVICE 中定义的值,即 sizeof(PCIDeviceClass)。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 typedef struct PCIDeviceClass { DeviceClass parent_class; void (*realize)(PCIDevice *dev, Error **errp); PCIUnregisterFunc *exit ; PCIConfigReadFunc *config_read; PCIConfigWriteFunc *config_write; uint16_t vendor_id; uint16_t device_id; uint8_t revision; uint16_t class_id; uint16_t subsystem_vendor_id; uint16_t subsystem_id; bool is_bridge; const char *romfile; } PCIDeviceClass;

PCIDeviceClass 表明了类属 PCI 设备的一些信息,如表示设备商信息的 vendor_id 和设备信息 device_id 以及读取 PCI 设备配置空间的 config_read 和 config_write 函数。值得注意的是,一个域是第一个成员 DeviceClass 的结构体,这描述的是属于“设备类型”的类型所具有的一些属性。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 struct ObjectClass { Type type; GSList *interfaces; const char *object_cast_cache[OBJECT_CLASS_CAST_CACHE]; const char *class_cast_cache[OBJECT_CLASS_CAST_CACHE]; ObjectUnparent *unparent; GHashTable *properties; }; typedef struct DeviceClass { ObjectClass parent_class; ... }

DeviceClass 定义了设备类型相关的基本信息以及基本的回调函数,第一个域也是表示其父类型的 Class,为 ObjectClass 。 ObjectClass 是所有类型的基础,会内嵌到对应的其他 Class 的第一个域中。

在 type_initialize 中会调用以下代码来对父类型所占的这部分空间进行初始化。

1 2 3 4 5 6 7 8 9 10 parent = type_get_parent(ti); if (parent) { memcpy (ti->class, parent->class, parent->class_size); } if (ti->class_init) { ti->class_init(ti->class, ti->class_data); }

对于 edu 设备来说这里的 class_init 为 edu_class_init。

1 2 3 4 5 6 7 8 9 10 11 12 13 static void edu_class_init (ObjectClass *class, void *data) { DeviceClass *dc = DEVICE_CLASS(class); PCIDeviceClass *k = PCI_DEVICE_CLASS(class); k->realize = pci_edu_realize; k->exit = pci_edu_uninit; k->vendor_id = PCI_VENDOR_ID_QEMU; k->device_id = 0x11e8 ; k->revision = 0x10 ; k->class_id = PCI_CLASS_OTHERS; set_bit(DEVICE_CATEGORY_MISC, dc->categories); }

类型转换 DEVICE_CLASS 和 PCI_DEVICE_CLASS 最终调用的函数为 object_class_dynamic_cast 。

函数首先通过 type_get_by_name 得到要转到的 TypeImpl,这里的 typename 是 TYPE_PCI_DEVICE 。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 ObjectClass *object_class_dynamic_cast (ObjectClass *class, const char *typename) { ObjectClass *ret = NULL ; TypeImpl *target_type; TypeImpl *type; if (!class) { return NULL ; } type = class->type; if (type->name == typename) { return class; } target_type = type_get_by_name(typename); if (!target_type) { return NULL ; } if (type->class->interfaces && type_is_ancestor(target_type, type_interface)) { int found = 0 ; GSList *i; for (i = class->interfaces; i; i = i->next) { ObjectClass *target_class = i->data; if (type_is_ancestor(target_class->type, target_type)) { ret = target_class; found++; } } if (found > 1 ) { ret = NULL ; } } else if (type_is_ancestor(type, target_type)) { ret = class; } return ret; }

以 edu 为例,type->name 是 edu,但是要转换到的却是 TYPE_PCI_DEVICE,所以会调用 type_is_ancestor("edu",TYPE_PCI_DEVICE) 来判断后者是否是前者的祖先。

在该函数中依次得到 edu 的父类型,然后判断是否与 TYPE_PCI_DEVICE 相等,由 edu 设备的 TypeInfo 可知其父类型为 TYPE_PCI_DEVICE,所以这个 type_is_ancestor 会成功,能够进行从 ObjectClass 到 PCIDeviceClass 的转换。这样就可以直接通过 (PCIDeviceClass*)ObjectClass 完成从 ObjectClass 到 PCIDeviceClass 的强制转换。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 static bool type_is_ancestor (TypeImpl *type, TypeImpl *target_type) { assert(target_type); while (type) { if (type == target_type) { return true ; } type = type_get_parent(type); } return false ; } static TypeImpl *type_get_parent (TypeImpl *type) { if (!type->parent_type && type->parent) { type->parent_type = type_get_by_name(type->parent); if (!type->parent_type) { fprintf (stderr , "Type '%s' is missing its parent '%s'\n" , type->name, type->parent); abort (); } } return type->parent_type; }

对象的构造与初始化 前面提到,首先每个类型指定一个 TypeInfo 注册到系统中,接着在系统运行初始化的时候会把 TypeInfo 转变成 TypeImple 放到一个哈希表中,这就是类型的注册。系统会对这个哈希表中的每一个类型进行初始化,主要是设置 TypeImpl 的一些域以及调用类型的 class_init 函数,这就是类型的初始化。现在系统中已经有了所有类型的信息并且这些类型的初始化函数已经调用了,接着会根据需要(如 QEMU 命令行指定的参数)创建对应的实例对象,也就是各个类型的 object 。

下面来分析指定 -device edu 命令的情况。在 main 函数中有这么一句话。

1 2 qemu_opts_foreach(qemu_find_opts("device" ), device_init_func, NULL , &error_fatal);

对每一个 -device 的参数,会调用 device_init_func 函数,该函数随即调用 qdev_device_add 进行设备的添加。通过 object_new 来构造对象,其调用链如下。

1 2 3 4 5 6 7 8 9 10 device_init_func | dev = qdev_device_add(opts, errp); | | dev = DEVICE(object_new(driver)); | | | TypeImpl *ti = type_get_by_name(typename); | | | object_new_with_type(ti); | | | | obj = g_malloc(type->instance_size); | | | | object_initialize_with_type(obj, type->instance_size, type); | | | | | object_init_with_type(obj, type); | | | | | object_post_init_with_type(obj, type); | | object_property_set_bool(OBJECT(dev), true , "realized" , &err);

object_initialize_with_type 的主要工作是对 object_init_with_type 和 object_post_init_with_type 进行调用,前者通过递归调用所有父类型的对象初始化函数和自身对象的初始化函数,后者调用 TypeImpl 的 instance_post_init 回调成员完成对象初始化之后的工作。下面以 edu 的 TypeInfo 为例进行介绍。

edu 的对象大小(instance_size)为 sizeof(EduState),所以实际上一个 edu 类型的对象是 EduState 结构体,每一个对象都会有一个 XXXState 与之对应,记录了该对象的相关信息,若 edu 是一个 PCI 设备,那么 EduState 里面就会有这个设备的一些信息,如中断信息、设备状态、使用的 MMIO 和 PIO 对应的内存区域等。object_init_with_type 函数中可以看到调用的参数都是一个 Object 。可以看出,对象之间实际也是有一种父对象与子对象的关系存在。与类型一样,QOM 中的对象也可以使用宏将一个指向 Object 对象的指针转换成一个指向子类对象的指针。转换过程与类型 ObjectClass 类似。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 struct Object { ObjectClass *class ; ObjectFree *free ; GHashTable *properties; uint32_t ref; Object *parent; }; struct DeviceState { Object parent_obj; }; struct PCIDevice { DeviceState qdev; }; typedef struct { PCIDevice pdev; } EduState;

这里可以看出,不同于类型信息和类型,object 是根据需要创建的,只有在命令行指定了设备或者是热插一个设备之后才会有 object 的创建。类型和对象之间是通过 Object 的 class 域联系在一起的。这是在 object_initialize_with_type 函数中通过 obj->class=type->class 实现的。

从上文可以看出,可以把 QOM 的对象构造分成 3 部分:

第一部分是类型的构造,通过 TypeInfo 构造一个 TypeImpl 的哈希表,这是在 main 之前完成的;

第二部分是类型的初始化,这是在 main 中进行的,这两部分都是全局的,也就是只要编译进去的 QOM 对象都会调用;

第三部分是类对象的构造,这是构造具体的对象实例,只有在命令行指定了对应的设备时,才会创建对象。

现在只是构造出了对象,并且调用了对象初始化函数,但是 EduState 里面的数据内容并没有填充,这个时候的 edu 设备状态并不是可用的,对设备而言还需要设置它的 realized 属性为 true 才行。在 qdev_device_add 函数的后面,还有这样一句:

1 object_property_set_bool(OBJECT(dev), true , "realized" , &err);

这句代码将 dev(也就是 edu 设备的 realized 属性)设置为 true ,这就涉及了 QOM 类和对象的另一个方面,即属性。

QOM 中的属性 在 QOM 中为了便于对对象进行管理,还给每种类型以及对象增加了属性。类属性存在于 ObjectClass 的 properties 域中,这个域是在类型初始化函数 type_initialize 中构造的。对象属性存放在 Object 的 properties 域中,这个域是在对象的初始化函数 object_initialize_with_type 中构造的。两者皆为一个哈希表,存着属性名字到 ObjectProperty 的映射。

属性由 ObjectProperty 表示。

1 2 3 4 5 6 7 8 9 10 11 12 13 struct ObjectProperty { gchar *name; gchar *type; gchar *description; ObjectPropertyAccessor *get; ObjectPropertyAccessor *set ; ObjectPropertyResolve *resolve; ObjectPropertyRelease *release; ObjectPropertyInit *init; void *opaque; QObject *defval; };

其中,name 表示名字;type 表示属性的类型,如有的属性是字符串,有的是 bool 类型,有的是 link 等其他更复杂的类型;get 、set 、resolve 等回调函数则是对属性进行操作的函数;opaque 指向一个具体的属性,如 BoolProperty 等。

每一种具体的属性都会有一个结构体来描述它。比如下面的 ·LinkProperty 表示 link 类型的属性,StringProperty 表示字符串类型的属性,BoolProperty 表示 bool 类型的属性。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 typedef struct { union { Object **targetp; Object *target; ptrdiff_t offset; }; void (*check)(const Object *, const char *, Object *, Error **); ObjectPropertyLinkFlags flags; } LinkProperty; typedef struct StringProperty { char *(*get)(Object *, Error **); void (*set )(Object *, const char *, Error **); } StringProperty; typedef struct BoolProperty { bool (*get)(Object *, Error **); void (*set )(Object *, bool , Error **); } BoolProperty;

以 Object 为例,属性相关结构如下:

属性的添加分为类属性的添加和对象属性的添加,以对象属性为例,它的属性添加是通过 object_property_add 接口完成的。段忽略了属性 name 中带有通配符 * 的情况,该函数内容如下:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 ObjectProperty * object_property_add (Object *obj, const char *name, const char *type, ObjectPropertyAccessor *get, ObjectPropertyAccessor *set , ObjectPropertyRelease *release, void *opaque, Error **errp) { ObjectProperty *prop; size_t name_len = strlen (name); if (object_property_find(obj, name, NULL ) != NULL ) { error_setg(errp, "attempt to add duplicate property '%s' to object (type '%s')" , name, object_get_typename(obj)); return NULL ; } prop = g_malloc0(sizeof (*prop)); prop->name = g_strdup(name); prop->type = g_strdup(type); prop->get = get; prop->set = set ; prop->release = release; prop->opaque = opaque; g_hash_table_insert(obj->properties, prop->name, prop); return prop; }

object_property_add 函数首先调用 object_property_find 来确认所插入的属性是否已经存在,确保不会添加重复的属性,接着分配一个 ObjectProperty 结构并使用参数进行初始化,然后调用 g_hash_table_insert 插入到对象的 properties 域中。

属性的查找通过 object_property_find 函数实现,代码如下。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 ObjectProperty *object_class_property_find (ObjectClass *klass, const char *name, Error **errp) { ObjectProperty *prop; ObjectClass *parent_klass; parent_klass = object_class_get_parent(klass); if (parent_klass) { prop = object_class_property_find(parent_klass, name, NULL ); if (prop) { return prop; } } prop = g_hash_table_lookup(klass->properties, name); if (!prop) { error_setg(errp, "Property '.%s' not found" , name); } return prop; }

这个函数首先调用 object_class_property_find 来确认自己所属的类以及所有父类都不存在这个属性,然后在自己的 properties 域中查找。

属性的设置是通过 object_property_set 来完成的,其只是简单地调用 ObjectProperty 的 set 函数。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 void object_property_set (Object *obj, Visitor *v, const char *name, Error **errp) { ObjectProperty *prop = object_property_find(obj, name, errp); if (prop == NULL ) { return ; } if (!prop->set ) { error_setg(errp, QERR_PERMISSION_DENIED); } else { prop->set (obj, v, name, prop->opaque, errp); } }

每一种属性类型都有自己的 set 函数,其名称为 property_set_XXX ,其中的 XXX 表示属性类型,如 bool、str、link 等。以 bool 为例,其 set 函数如下。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 static void property_set_bool (Object *obj, Visitor *v, const char *name, void *opaque, Error **errp) { BoolProperty *prop = opaque; bool value; Error *local_err = NULL ; visit_type_bool(v, name, &value, &local_err); if (local_err) { error_propagate(errp, local_err); return ; } prop->set (obj, value, errp); }

可以看到,其调用了具体属性(BoolProperty)的 set 函数,这是在创建这个属性的时候指定的。

QEMU 内存虚拟化 QEMU 内存结构 MemoryRegion 抽象了 一个地址空间中的一段范围 ,既可以是可读写的 RAM ,也可以是由回调实现的 MMIO ,还可以是I/O 端口空间的桥接 、别名(Alias) 、IOMMU 入口 、只读 ROM/ROMD ,或者纯容器(Container/Root) 。它们共同组成 无环图(DAG) 的内存映射视图,最终被“扁平化”成 AddressSpace 的映射供 CPU/设备访问。

该结构体定义于 include/exec/memory.h 当中:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 struct MemoryRegion { Object parent_obj; bool romd_mode; bool ram; bool subpage; bool readonly; bool nonvolatile; bool rom_device; bool flush_coalesced_mmio; bool global_locking; uint8_t dirty_log_mask; bool is_iommu; RAMBlock *ram_block; Object *owner; const MemoryRegionOps *ops; void *opaque; MemoryRegion *container; Int128 size; hwaddr addr; void (*destructor)(MemoryRegion *mr); uint64_t align; bool terminates; bool ram_device; bool enabled; bool warning_printed; uint8_t vga_logging_count; MemoryRegion *alias; hwaddr alias_offset; int32_t priority; QTAILQ_HEAD(, MemoryRegion) subregions; QTAILQ_ENTRY(MemoryRegion) subregions_link; QTAILQ_HEAD(, CoalescedMemoryRange) coalesced; const char *name; unsigned ioeventfd_nb; MemoryRegionIoeventfd *ioeventfds; };

MemoryRegion 的成员函数被封装在函数表 MemoryRegionOps 当中:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 struct MemoryRegionOps { uint64_t (*read)(void *opaque, hwaddr addr, unsigned size); void (*write)(void *opaque, hwaddr addr, uint64_t data, unsigned size); MemTxResult (*read_with_attrs)(void *opaque, hwaddr addr, uint64_t *data, unsigned size, MemTxAttrs attrs); MemTxResult (*write_with_attrs)(void *opaque, hwaddr addr, uint64_t data, unsigned size, MemTxAttrs attrs); enum device_endian endianness ; struct { unsigned min_access_size; unsigned max_access_size; bool unaligned; bool (*accepts)(void *opaque, hwaddr addr, unsigned size, bool is_write, MemTxAttrs attrs); } valid; struct { unsigned min_access_size; unsigned max_access_size; bool unaligned; } impl; };

MemoryRegionOps 中的 read、write 回调函数只有在命中 IO 型区域(MMIO/ROM‑device/PMIO) 时才会调用,否则直接直接对宿主内存读写。

1 2 3 4 5 6 7 Guest CPU 访存 │ ▼ AddressSpace(地址簿) │ 查表定位 ├──► MemoryRegion = RAM/ROM ──► 直接读/写宿主内存 └──► MemoryRegion = IO(设备) ─► 调用 ops.read / ops.write(你的设备代码)

IO 型内存注册 memory_region_init_io memory_region_init_io() 初始化 一个 MemoryRegion,并不会“挂到总线”或“映射给来宾”。真正对外可见还要交给 pci_register_bar() 或 memory_region_add_subregion() 等去“导出”。

1 2 3 4 5 6 7 void memory_region_init_io (MemoryRegion *mr, Object *owner, const MemoryRegionOps *ops, void *opaque, const char *name, uint64_t size) ;

返回值 :void(无返回值)

参数含义 :

mr:你要初始化的 MemoryRegion 实例(通常是设备状态结构里的一个成员)。

owner:QOM 拥有者,一般传 OBJECT(dev) 或 OBJECT(&s->pdev.qdev),用于生命周期管理/可视化。

ops:回调表,定义了读写函数等属性:

1 2 3 4 5 6 typedef struct MemoryRegionOps { uint64_t (*read)(void *opaque, hwaddr addr, unsigned size); void (*write)(void *opaque, hwaddr addr, uint64_t data, unsigned size); enum device_endian endianness ; } MemoryRegionOps;

opaque:回调里透传给你(设备实例指针,常传 s)。

name:调试/监控友好的区域名(如 "strng-mmio")。

size:区域大小(字节)。QEMU 会用它做边界检查 ,超出范围的访问不会进入你的 ops。

pci_register_bar 把 memory 绑定到设备配置空间的 BARregion_num;当来宾写 BAR 寄存器确定映射地址后,访问将由 QEMU 转发到 ops->read/write。边界由 memory->size 保证 ,越界访问不会进入回调。

1 2 3 4 5 void pci_register_bar (PCIDevice *dev, int region_num, uint8_t type, MemoryRegion *memory) ;

返回值 :void(无返回值)

参数含义 :

dev:PCIDevice*,你的 PCI 设备实例(通常是 &s->pdev)。

region_num:BAR 编号,0..5(普通设备最多 6 个 BAR;ROM 另算)。

type:BAR 类型/标志的组合:

PCI_BASE_ADDRESS_SPACE_MEMORY = 0x00(内存映射 MMIO)

PCI_BASE_ADDRESS_SPACE_IO = 0x01(I/O 端口 PMIO)

可与以下标志 OR 用(用于 memory BAR):

PCI_BASE_ADDRESS_MEM_TYPE_64(64 位 BAR,会消耗连续两个 BAR 槽)PCI_BASE_ADDRESS_MEM_PREFETCH(可预取)

memory:已经 memory_region_init_io() 好的 MemoryRegion。注册后,来宾对该 BAR 对应的地址空间访问会路由到 memory 的 ops。

IO 型内存读写 下面这两个原型就是 QEMU MemoryRegionOps 里“IO 类型内存”(也就是设备的 MMIO/PIO BAR)的访问回调,用来响应来 自客体 CPU 的一次总线事务(bus transaction):

1 2 uint64_t (*read)(void *opaque, hwaddr addr, unsigned size);void (*write)(void *opaque, hwaddr addr, uint64_t data, unsigned size);

opaquememory_region_init_io(..., &ops, opaque, ...) 里传入的设备状态指针,一般是你的 DeviceState/PCIDevice 的私有结构指针。回调里先把它强转回你的设备结构,然后读写寄存器/状态。

addr(类型 hwaddr)偏移 ,相对于该 MemoryRegion 的起始地址(也就是相对于 BAR 的起点)。不是系统物理地址。hwaddr 是面向“客体地址宽度”的无符号整型,足以容纳 64 位偏移。

size(单位:字节)MemoryRegionOps 的“可接受/实现的访问宽度”设定决定;不支持的宽度,QEMU 会拆成更小的多次调用,或直接拒绝访问,取决于你的配置)。

data(仅写回调)size * 8 位。你在写入设备寄存器时应据此掩码并对齐。

read 的返回值低 size * 8 位 承载。不要做符号扩展。对齐/字节序由 MemoryRegionOps 的 endianness 和访问宽度共同决定。

小结:一次 CPU 对设备寄存器的 load/store → QEMU 解析后调用你的 read/write,你依据 addr/size 在寄存器空间里取/改值并返回/完成。

内存操作函数 AddressSpace 通用读写 1 2 3 4 5 6 7 8 9 MemTxResult address_space_read (AddressSpace *as, hwaddr addr, MemTxAttrs attrs, void *buf, size_t len) ;MemTxResult address_space_write (AddressSpace *as, hwaddr addr, MemTxAttrs attrs, const void *buf, size_t len) ;MemTxResult address_space_rw (AddressSpace *as, hwaddr addr, MemTxAttrs attrs, void *buf, size_t len, bool is_write) ;

参数说明

as:要访问的地址空间 。常见有:

系统物理内存(system memory)的 AddressSpace(例如 &address_space_memory);

I/O 地址空间;

经过 IOMMU 翻译后的 DMA AddressSpace (比如为某个总线/设备创建的 DMA AS)。

addr:在该 AddressSpace 内的起始物理地址/IO 地址 。

attrs:事务属性 (MemTxAttrs),通常写 MEMTXATTRS_UNSPECIFIED。它会随访问传递,供内存监听器、IOMMU 等子系统解读(比如是否可被合并、缓存属性、发起者信息等,具体随目标体系结构/设备而定)。

buf / len:读/写的用户缓冲区与长度;读时把目标内容拷贝到 buf,写时从 buf 拷贝到目标。

is_write:仅对 address_space_rw(),true=写,false=读。

返回值(错误处理)

返回 MemTxResult:成功 为“OK”(不同版本的枚举名略有差别,但你可以把“非 OK”都当错误处理),失败表示访问异常、解码失败(地址无映射/被拒)、或设备侧报错。

实践建议:判是否为 OK ,错误时在设备里置位 DMA 错误、触发中断或按设备规范处理。

使用场景

你已经知道 要访问哪个 AddressSpace(例如已拿到“某设备的 DMA 地址空间”),并希望以统一 API 发起读/写。

dma_memory_read / dma_memory_write(设备发起 DMA 时优先用)1 2 3 4 5 6 7 8 9 int dma_memory_read (AddressSpace *as, dma_addr_t addr, void *buf, dma_addr_t len) ;int dma_memory_write (AddressSpace *as, dma_addr_t addr, const void *buf, dma_addr_t len) ;MemTxResult dma_memory_read_with_attrs (AddressSpace *as, dma_addr_t addr, void *buf, dma_addr_t len, MemTxAttrs attrs) ;MemTxResult dma_memory_write_with_attrs (AddressSpace *as, dma_addr_t addr, const void *buf, dma_addr_t len, MemTxAttrs attrs) ;

参数说明

as:DMA 使用的 AddressSpace 。若系统存在 IOMMU,请确保这里传的是IOMMU 后的 DMA AS (否则就绕过了 IOMMU,不符合真实硬件)。addr:DMA 地址 (设备视角下的地址)。buf / len:同上。attrs:同上;大多数设备用 MEMTXATTRS_UNSPECIFIED 就好。

返回值

简化版返回 int(0 成功,<0 失败);*_with_attrs 返回 MemTxResult。

DMA(Direct Memory Access,直接内存访问) 是指外设 (比如网卡/存储/显卡/PCIe 设备)绕过 CPU ,直接在来宾的内存地址空间里读/写数据 的一种机制。

在 QEMU 设备模型里,“设备做 DMA”= 你的设备代码主动去读/写 Guest(或经 IOMMU 翻译后的 I/O 虚拟地址,IOVA)里的缓冲区。

CPU 访存 :Guest 的 CPU 执行指令触发访存(load/store),QEMU 根据地址落到 RAM 或 MMIO;MMIO 会调用你的 MemoryRegionOps.read/write 回调。DMA 访存 :设备本身 发起内存传输(比如把网卡收到的数据写到来宾内存中的 ring buffer),在 QEMU 里表现为设备模型主动调用 dma_memory_read/write(或 pci_dma_read/write)。

PCI 专用:pci_dma_read / pci_dma_write 这两个函数用于PCI 设备发起 DMA :从设备视角用 IOVA/DMA 地址 去读/写来宾内存的数据。它们会根据 dev 自动选择正确的 DMA AddressSpace (考虑 IOMMU/ATS 等),比你自己拿 AddressSpace 更不容易出错。

1 2 int pci_dma_read (PCIDevice *dev, dma_addr_t addr, void *buf, dma_addr_t len) ;int pci_dma_write (PCIDevice *dev, dma_addr_t addr, const void *buf, dma_addr_t len) ;

参数说明

dev: 发起 DMA 的 PCIDevice *(你的设备对象)。

addr: dma_addr_t,设备看到的 DMA 地址 (通常是 IOVA;没有 IOMMU 时等同于来宾物理地址)。

buf: 主机侧缓冲区指针。

pci_dma_read:输出缓冲 (把来宾内存读到这里)。pci_dma_write:输入缓冲 (把这里的数据写到来宾内存)。

len: 传输字节数(dma_addr_t 类型以便支持 64 位长度)。

返回值

0:整段传输 成功MemTxResult == MEMTX_OK)。

非 0(通常为 -1) :传输失败 (底层不是 MEMTX_OK)。

不保证设置 errno;不要 依赖 errno。

失败原因可能是:IOMMU 翻译失败/权限拒绝、地址未映射(解码失败)、目标 MemoryRegion 报错、越界等。

没有“部分成功”的返回 :要么成功完成 len 字节,要么失败(如果你需要部分长度语义,就改用 address_space_map/unmap 循环搬运,或把大块拆小分段重试)。

特点

会基于 dev 选择正确的 DMA AddressSpace (考虑 IOMMU/ATS 等),避免你手动找 AS 出错。

语义与 dma_memory_* 等价,但更贴近“PCI 设备发起 DMA”的常见场景。

另外有的版本的 QEMU 还会提供带 MemTxResult 属性的 pci_dma_* 函数。

1 2 3 4 5 MemTxResult pci_dma_read_with_attrs (PCIDevice *dev, dma_addr_t addr, void *buf, dma_addr_t len, MemTxAttrs attrs) ;MemTxResult pci_dma_write_with_attrs (PCIDevice *dev, dma_addr_t addr, const void *buf, dma_addr_t len, MemTxAttrs attrs) ;

对于这种形式的 API,返回值:

cpu_physical_memory_*cpu_physical_memory_* 是 QEMU 的“上帝视角”直接访问来宾“系统物理内存地址空间” (system_memory)的工具函数。

它们不经过 IOMMU 、不做设备权限检查 、也不触发设备的 MMIO 回调 。

典型用途:monitor/调试/固件加载/快照工具 等“宿主侧主动”对 Guest 物理内存做读写。

不要 用它们在设备模型 里模拟 DMA/寄存器访问(会偏离真实硬件路径)。

1 2 3 4 5 6 void cpu_physical_memory_read (hwaddr addr, void *buf, size_t len) ;void cpu_physical_memory_write (hwaddr addr, const void *buf, size_t len) ;void cpu_physical_memory_rw (hwaddr addr, void *buf, size_t len, int is_write) ;void *cpu_physical_memory_map (hwaddr addr, hwaddr *plen, int is_write) ;void cpu_physical_memory_unmap (void *host_ptr, hwaddr len, int is_write, hwaddr access_len) ;

参数说明

addr: hwaddr 目标来宾物理地址 (system_memory 的物理地址,不是 IOVA,不是虚拟地址)。buf: void* / const void* 主机侧缓冲区指针。read/rw(is_write=0) 为输出 缓冲,write/rw(is_write=1) 为输入 缓冲。len: size_t 读/写的字节数 。可以很大,函数内部会自动跨页/跨 region 逐段处理。is_write: int(仅 rw)0=读,非 0=写。

返回/错误行为

这些函数没有返回值 ,不会把错误以返回码形式告诉你。

当访问到未映射/被拒绝的区域时,不同版本/路径一般会:

读 :把对应字节视作 0 (复制 0 到 buf 的那段);写 :丢弃 那部分写入(相当于没写成功)。

因此用于调试/加载 没问题,但 不要 拿它判断“访问是否真的成功”,也不要用来模拟设备行为。

内存地址转换 Linux 在用户态 (有高权限)可以用 /proc/<pid>/pagemap 获取内存地址(虚拟地址) 对应的物理地址 。

Linux 提供 pagemap 接口,可把某进程的虚拟页 映射到页帧号 PFN ,再算出物理地址:

物理地址 = PFN × 页大小 + 页内偏移 。

自 Linux 4.0 起,未授予 CAP_SYS_ADMIN 时 PFN 会被屏蔽/置零 (防范 Rowhammer 等攻击,4.0–4.1 未授权直接 open 失败,4.2+ 则 PFN 字段置零),因此要么用 root、要么给程序授予该能力,否则得不到 PFN。

pagemap 64 位项的位义(简化)如下:

bit63=present,

bit62=swapped,

bits 0–54 为 PFN(在 present 时有效)

内存地址(虚拟地址) 转换物理地址 的具体步骤为:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 #include <stdint.h> #include <stdio.h> #include <unistd.h> #include <fcntl.h> #include <sys/mman.h> #include <errno.h> static uint64_t virt_to_phys (void *vaddr) { long pagesize = sysconf(_SC_PAGESIZE); uint64_t va = (uint64_t )vaddr; uint64_t page_index = va / pagesize; uint64_t offset = page_index * sizeof (uint64_t ); int fd = open("/proc/self/pagemap" , O_RDONLY); if (fd < 0 ) return 0 ; uint64_t entry = 0 ; ssize_t n = pread(fd, &entry, sizeof (entry), offset); close(fd); if (n != sizeof (entry)) return 0 ; if (!(entry & (1ULL << 63 )) || (entry & (1ULL << 62 ))) { errno = EFAULT; return 0 ; } uint64_t pfn = entry & ((1ULL << 55 ) - 1 ); return (pfn * pagesize) + (va % pagesize); }

确保页已驻留 (否则 present=0):触碰一次该地址或用 mlock() 将其锁入内存。打开 /proc/self/pagemap(或 /proc/<pid>/pagemap),按“页索引×8 ”偏移读取一个 64 位条目;偏移和读大小必须是 8 的倍数。

检查 bit63(present)。若不在内存或 bit62(swapped)为 1,就无法得到当前物理地址。

取 PFN(条目低 55 位)。

计算物理地址:phys = (PFN << PAGE_SHIFT) | (va & (page_size-1))。

mmap 本身不会立即分配物理页 ,Linux 默认按需分配(首次访问触发缺页才真正拿到物理页)。因此直接 mmap 分配的匿名页通过 /proc/self/pagemap 查询不到对应的物理地址。

mmap 时加 MAP_POPULATE(“预触发”) 对于可写的、私有、匿名映射 (典型组合:MAP_PRIVATE|MAP_ANONYMOUS + PROT_READ|PROT_WRITE),Linux 在处理 MAP_POPULATE 时,会走“写缺页 ”的预触发路径,把每一页都像被写过一样 提前 fault 进来,从而为每一页分配匿名物理页 。

1 2 3 #include <sys/mman.h> void *p = mmap(NULL , len, PROT_READ|PROT_WRITE, MAP_PRIVATE|MAP_ANONYMOUS|MAP_POPULATE, -1 , 0 );

QEMU 设备分析 PCI 设备 设备实例定义 首先是设备的 State 结构体,该结构体即设备的 Object 中自身的部分,包含了设备自身定义的全部相关结构。关于设备的操作都是围绕这个结构体展开的。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 #define TYPE_PCI_EDU_DEVICE "edu" #define EDU(obj) OBJECT_CHECK(EduState, obj, TYPE_PCI_EDU_DEVICE) #define FACT_IRQ 0x00000001 #define DMA_IRQ 0x00000100 #define DMA_START 0x40000 #define DMA_SIZE 4096 typedef struct { PCIDevice pdev; MemoryRegion mmio; QemuThread thread; QemuMutex thr_mutex; QemuCond thr_cond; bool stopping; uint32_t addr4; uint32_t fact; #define EDU_STATUS_COMPUTING 0x01 #define EDU_STATUS_IRQFACT 0x80 uint32_t status; uint32_t irq_status; #define EDU_DMA_RUN 0x1 #define EDU_DMA_DIR(cmd) (((cmd) & 0x2) >> 1) # define EDU_DMA_FROM_PCI 0 # define EDU_DMA_TO_PCI 1 #define EDU_DMA_IRQ 0x4 struct dma_state { dma_addr_t src; dma_addr_t dst; dma_addr_t cnt; dma_addr_t cmd; } dma; QEMUTimer dma_timer; char dma_buf[DMA_SIZE]; uint64_t dma_mask; } EduState;

设备类型定义 其次是设备的 TypeInfo ,重点关注其中的 instance_init,class_init等初始化函数。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 static void pci_edu_register_types (void ) { static InterfaceInfo interfaces[] = { { INTERFACE_CONVENTIONAL_PCI_DEVICE }, { }, }; static const TypeInfo edu_info = { .name = TYPE_PCI_EDU_DEVICE, .parent = TYPE_PCI_DEVICE, .instance_size = sizeof (EduState), .instance_init = edu_instance_init, .class_init = edu_class_init, .interfaces = interfaces, }; type_register_static(&edu_info); } type_init(pci_edu_register_types)

instance_size 告诉 QOM:创建这个对象时需要分配多大的一块内存(也就是 EduState 的大小)。class_init 在类级别 设置默认回调(例如把 PCIDeviceClass::realize 指到 pci_edu_realize)。instance_init 在实例级别 设字段默认值、注册 QOM 属性等(必须不失败)。

当你在命令行 -device edu 或在代码里新增这个设备时,QEMU 会:

分配一块大小为 sizeof(EduState) 的零清内存;

构造父类子对象(因为 EduState 的第一个成员是 PCIDevice pdev;,这就是“内嵌继承”);

调用 edu_instance_init() 给实例字段设缺省值、注册属性(如 dma_mask)。

设备初始化操作 从设备的 class_init 和 instance_init 等初始化函数中我们可以获取到设备的相关信息。其中 realize 和 exit 函数定义了一部分 Object 初始化和销毁操作。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 static void edu_instance_init (Object *obj) { EduState *edu = EDU(obj); edu->dma_mask = (1UL << 28 ) - 1 ; object_property_add_uint64_ptr(obj, "dma_mask" , &edu->dma_mask, OBJ_PROP_FLAG_READWRITE, NULL ); } static void edu_class_init (ObjectClass *class, void *data) { DeviceClass *dc = DEVICE_CLASS(class); PCIDeviceClass *k = PCI_DEVICE_CLASS(class); k->realize = pci_edu_realize; k->exit = pci_edu_uninit; k->vendor_id = PCI_VENDOR_ID_QEMU; k->device_id = 0x11e8 ; k->revision = 0x10 ; k->class_id = PCI_CLASS_OTHERS; set_bit(DEVICE_CATEGORY_MISC, dc->categories); }

realize 和 exit 函数定义的是对象初始化和销毁中可能会失败的操作。

class_init(类初始化,ObjectClass 级) :设定类的默认虚函数/回调 (比如把 DeviceClass::realize 指向你的实现),不触碰实例数据。对象尚未出现。

设定/覆盖虚函数:dc->realize、dc->unrealize、desc、user_creatable 等。

静态属性数组(device_class_set_props() 给 DeviceClass.props_)。

instance_init(实例初始化,Object 实例级,必须不失败) :新建对象后,给实例字段设默认值、创建子对象的“壳”(object_initialize)、注册 QOM 属性 等;不能失败 。此时不 把设备接到总线,也不 占用全局资源。

设实例缺省值;

用 object_property_add*() 注册 QOM 属性 (这样 --device xyz,help/device-list-properties 才看得到/可设置);通过 object_initialize() 创建子对象的壳 (注意:不是在这里 realize 子对象)。

realize(实现,可以失败) :把实例接入系统 :校验用户已设置的属性、在总线上登记、映射 BAR/MMIO、连 IRQ、申请可能失败的资源;可以失败 ,需通过 errp 报错。可选的 unrealize 负责撤销。

依据属性 做校验;

接总线 、分配并注册 BAR/MMIO/PIO、连 IRQ、把子对象逐个 realize;申请任何可能失败的外部资源;必要时通过 Error **errp 返回错误。

设备内存的注册多出现在 realize 函数中,例如 edu 中的 memory_region_init_io 和 pci_register_bar 注册了一块 MMIO 类型的内存。我们需要重点关注 MemoryRegionOps 结构体 edu_mmio_ops 。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 static void pci_edu_realize (PCIDevice *pdev, Error **errp) { EduState *edu = EDU(pdev); uint8_t *pci_conf = pdev->config; pci_config_set_interrupt_pin(pci_conf, 1 ); if (msi_init(pdev, 0 , 1 , true , false , errp)) { return ; } timer_init_ms(&edu->dma_timer, QEMU_CLOCK_VIRTUAL, edu_dma_timer, edu); qemu_mutex_init(&edu->thr_mutex); qemu_cond_init(&edu->thr_cond); qemu_thread_create(&edu->thread, "edu" , edu_fact_thread, edu, QEMU_THREAD_JOINABLE); memory_region_init_io(&edu->mmio, OBJECT(edu), &edu_mmio_ops, edu, "edu-mmio" , 1 * MiB); pci_register_bar(pdev, 0 , PCI_BASE_ADDRESS_SPACE_MEMORY, &edu->mmio); } static void pci_edu_uninit (PCIDevice *pdev) { EduState *edu = EDU(pdev); qemu_mutex_lock(&edu->thr_mutex); edu->stopping = true ; qemu_mutex_unlock(&edu->thr_mutex); qemu_cond_signal(&edu->thr_cond); qemu_thread_join(&edu->thread); qemu_cond_destroy(&edu->thr_cond); qemu_mutex_destroy(&edu->thr_mutex); timer_del(&edu->dma_timer); msi_uninit(pdev); }

edu_mmio_ops 结构体定义如下,可以看到 edu 设备自定义的读写函数 edu_mmio_read 和 edu_mmio_write 。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 static const MemoryRegionOps edu_mmio_ops = { .read = edu_mmio_read, .write = edu_mmio_write, .endianness = DEVICE_NATIVE_ENDIAN, .valid = { .min_access_size = 4 , .max_access_size = 8 , }, .impl = { .min_access_size = 4 , .max_access_size = 8 , }, };

QEMUTimer QEMUTimer 是 QEMU 事件循环里的软件定时器对象 :挂在某个 QEMUClock 上,按指定“时钟”的时间线到点就回调你的处理函数,用来驱动设备里的超时、周期性中断等逻辑。

QEMU 有四条时间线,你创建定时器时要选其一:realtime(宿主墙钟)、host(宿主单调时钟)、virtual(只在 guest 运行时前进)、virtual_rt(按 guest 速度走但用于客体外模块)。做设备建模一般用 virtual,因为它会在 VM 暂停/断点时一起停,从而保持确定性。

简单来说 QEMUTimer = “挂在某条 QEMUClock 时间线上的回调闹钟” 。设备模型里写寄存器→计算到期点→timer_mod()→到点发 IRQ/做 DMA,就是它的日常工作流。

由于 QEMUTimer 会定期回调一些指针结构,因此在 QEMU 逃逸中我们通常选择通过修改 QEMUTimer 相关结构来劫持程序执行流。

QEMUTimer 相关结构 相关函数和结构如下:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 struct QEMUTimerList { QEMUClock *clock; QemuMutex active_timers_lock; QEMUTimer *active_timers; QLIST_ENTRY(QEMUTimerList) list ; QEMUTimerListNotifyCB *notify_cb; void *notify_opaque; QemuEvent timers_done_ev; }; typedef struct QEMUClock { QLIST_HEAD(, QEMUTimerList) timerlists; QEMUClockType type; bool enabled; } QEMUClock; struct QEMUTimer { int64_t expire_time; QEMUTimerList *timer_list; QEMUTimerCB *cb; void *opaque; QEMUTimer *next; int attributes; int scale; }; struct QemuMutex { pthread_mutex_t lock; #ifdef CONFIG_DEBUG_MUTEX const char *file; int line; #endif bool initialized; }; typedef enum { QEMU_CLOCK_REALTIME = 0 , QEMU_CLOCK_VIRTUAL = 1 , QEMU_CLOCK_HOST = 2 , QEMU_CLOCK_VIRTUAL_RT = 3 , QEMU_CLOCK_MAX } QEMUClockType; struct QEMUTimerListGroup { QEMUTimerList *tl[QEMU_CLOCK_MAX]; }; extern QEMUTimerListGroup main_loop_tlg;

各个结构之间的关系如下:

classDiagram

direction LR

class QEMUTimer {

expire_time : int64_t (0x00)

timer_list : QEMUTimerList* (0x08)

cb : QEMUTimerCB* (0x10)

opaque : void* (0x18)

next : QEMUTimer* (0x20)

attributes : int (0x28)

scale : int (0x2C)

size : 0x30

}

class QemuMutex {

lock : pthread_mutex_t (0x00, 0x28)

initialized : bool (0x28)

size : 0x30

}

class QEMUClock {

timerlists_lh_first : QEMUTimerList* (0x00)

type : QEMUClockType (0x08)

enabled : bool (0x0C)

size : 0x10

}

class QEMUTimerList {

clock : QEMUClock* (0x00)

active_timers_lock : QemuMutex (0x08, 0x30)

active_timers : QEMUTimer* (0x38)

list.le_next : QEMUTimerList* (0x40)

list.le_prev : QEMUTimerList** (0x48)

notify_cb : QEMUTimerListNotifyCB* (0x50)

notify_opaque : void* (0x58)

timers_done_ev : QemuEvent (0x60, 0x08)

size : 0x68

}

class QEMUTimerListGroup {

tl_0_REALTIME : QEMUTimerList* (0x00)

tl_1_VIRTUAL : QEMUTimerList* (0x08)

tl_2_HOST : QEMUTimerList* (0x10)

tl_3_VIRTUAL_RT: QEMUTimerList* (0x18)

size : 0x20

}

QEMUClock o-- QEMUTimerList : timerlists

QEMUTimerList --> QEMUClock : clock

QEMUTimerList o-- QEMUTimer : active_timers

QEMUTimer --> QEMUTimer : next

QEMUTimer --> QEMUTimerList : timer_list

QEMUTimerList --> QemuMutex : active_timers_lock

QEMUTimerListGroup o-- QEMUTimerList : tl_*

QEMUTimer 使用 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 typedef struct { QEMUTimer *tmr; int64_t period_ns; } MyDev; static void my_cb (void *opaque) { MyDev *s = opaque; } static void my_realize (MyDev *s) { s->tmr = timer_new_ns(QEMU_CLOCK_VIRTUAL, my_cb, s); s->period_ns = 5 * 1000 * 1000 ; int64_t now = qemu_clock_get_ns(QEMU_CLOCK_VIRTUAL); timer_mod_ns(s->tmr, now + s->period_ns); } static void my_unrealize (MyDev *s) { timer_free(s->tmr); }

timer_new_* 函数创建一个 QEMUTimer 结构。最终都会调用到 timer_init_full 函数。

pwndbg> timer_init_full (ts=0x55555580e330 <_start>, timer_list_group=0x7fffffffd9e0, type=QEMU_CLOCK_REALTIME, scale=48, attributes=256, cb=0x7ffff76bab95 <__libc_calloc+133>, opaque=0x0) at ../util/qemu-time 1

#1 0x0000555555c914e2 in timer_new_full (timer_list_group=0x0, type=QEMU_CLOCK_VIRTUAL_RT, scale=1, attributes=0, cb=0x555555c916c5 <cpu_throttle_timer_tick>, opaque=0x0) at /home/flyyy/Desktop/qemu-vul/q 4

#2 0x0000555555c91527 in timer_new (type=QEMU_CLOCK_VIRTUAL_RT, scale=1, cb=0x555555c916c5 <cpu_throttle_timer_tick>, opaque=0x0) at /home/flyyy/Desktop/qemu-vul/qemu-5.2.0-rc4/include/qemu/timer.h :544

#3 0x0000555555c91553 in timer_new_ns (type=QEMU_CLOCK_VIRTUAL_RT, cb=0x555555c916c5 <cpu_throttle_timer_tick>, opaque=0x0) at /home/flyyy/Desktop/qemu-vul/qemu-5.2.0-rc4/include/qemu/timer.h :562

#4 0x0000555555c9189b in cpu_throttle_init () at ../softmmu/cpu-throttle.c :120

#5 0x0000555555c41869 in cpu_timers_init () at ../softmmu/cpu-timers.c :278

#6 0x0000555555be5b99 in qemu_init (argc=18, argv=0x7fffffffdda8, envp=0x7fffffffde40) at ../softmmu/vl.c :4256

#7 0x000055555580e445 in main (argc=18, argv=0x7fffffffdda8, envp=0x7fffffffde40) at ../softmmu/main.c :49

#8 0x00007ffff7643083 in __libc_start_main (main=0x55555580e419 <main>, argc=18, argv=0x7fffffffdda8, init=<optimized out>, fini=<optimized out>, rtld_fini=<optimized out>, stack_end=0x7fffffffdd98) at .. 8

#9 0x000055555580e35e in _start ()该函数初始化 QEMUTimer 结构,其中 expire_time 被设置为 -1,因此默认不会调用回调函数。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 void timer_init_full (QEMUTimer *ts, QEMUTimerListGroup *timer_list_group, QEMUClockType type, int scale, int attributes, QEMUTimerCB *cb, void *opaque) { if (!timer_list_group) { timer_list_group = &main_loop_tlg; } ts->timer_list = timer_list_group->tl[type]; ts->cb = cb; ts->opaque = opaque; ts->scale = scale; ts->attributes = attributes; ts->expire_time = -1 ; }

之后 timer_mod_ns() 把定时器插入按到期时间排序 的链表;如果它成了新的表头 ,框架会打断 poll 并重算 deadline (rearm),以便尽快触发。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 void timer_mod_ns (QEMUTimer *ts, int64_t expire_time) { QEMUTimerList *timer_list = ts->timer_list; bool rearm; qemu_mutex_lock(&timer_list->active_timers_lock); timer_del_locked(timer_list, ts); rearm = timer_mod_ns_locked(timer_list, ts, expire_time); qemu_mutex_unlock(&timer_list->active_timers_lock); if (rearm) { timerlist_rearm(timer_list); } } static bool timer_mod_ns_locked (QEMUTimerList *timer_list, QEMUTimer *ts, int64_t expire_time) { QEMUTimer **pt, *t; pt = &timer_list->active_timers; for (;;) { t = *pt; if (!timer_expired_ns(t, expire_time)) { break ; } pt = &t->next; } ts->expire_time = MAX(expire_time, 0 ); ts->next = *pt; qatomic_set(pt, ts); return pt == &timer_list->active_timers; }

QEMUTimerList 回调 QEMUTimerList 的 notify_cb 回调是唤醒/通知事件循环 的回调,不处理业务。该回调函数的定义如下:

1 typedef void QEMUTimerCB (void *opaque) ;

它的职责是当“最早到期点 发生变化,或者某条时钟被重新启用”时,打断 poll/epoll 睡眠 并触发重新计算 deadline 。如果未设置 notify_cb,默认走 qemu_notify_event()。

典型触发路径是 “最早到期点变了 → 需要重置 poll 超时/打断睡眠” 。例如当对一个定时器执行 timer_mod*(),且它成为表头(新的最早到期) 或从无到有 :timer_mod*() → timer_mod_ns_locked() 插入排序 → 返回需要 rearm → timerlist_rearm() → **timerlist_notify() → notify_cb(opaque)**(若未设置则 qemu_notify_event())。

pwndbg> qemu_timer_notify_cb (opaque=0x1c1768ab8f0, type=QEMU_CLOCK_REALTIME) at ../softmmu/cpu-timers.c :243

#1 0x0000555555e9c62d in timerlist_notify (timer_list=0x55555691b1e0) at ../util/qemu-timer.c :300

#2 0x0000555555e9c9b9 in timerlist_rearm (timer_list=0x55555691b1e0) at ../util/qemu-timer.c :424

#3 0x0000555555e9cae2 in timer_mod_ns (ts=0x55555696bfa0, expire_time=895342000368) at ../util/qemu-timer.c :452

#4 0x0000555555e9cc28 in timer_mod (ts=0x55555696bfa0, expire_time=895342000368) at ../util/qemu-timer.c :481

#5 0x0000555555b918ce in apic_timer_update (s=0x55555689d800, current_time=893574944608) at ../hw/intc/apic.c :623

#6 0x0000555555b91f4d in apic_mem_write (opaque=0x55555689d800, addr=896, val=110440984, size=4) at ../hw/intc/apic.c :826

#7 0x0000555555c08105 in memory_region_write_accessor (mr=0x55555689d890, addr=896, value=0x7ffff504be98, size=4, shift=0, mask=4294967295, attrs=...) at ../softmmu/memory.c :491

#8 0x0000555555c0833c in access_with_adjusted_size (addr=896, value=0x7ffff504be98, size=4, access_size_min=1, access_size_max=4, access_fn=0x555555c08018 <memory_region_write_accessor>, mr=0x55555689d8902

#9 0x0000555555c0b3ef in memory_region_dispatch_write (mr=0x55555689d890, addr=896, data=110440984, op=MO_32, attrs=...) at ../softmmu/memory.c :1501

#10 0x0000555555bc8b0c in io_writex (env=0x5555569448d0, iotlbentry=0x7fffa868c1e0, mmu_idx=2, val=110440984, addr=18446744073699054464, retaddr=140736193352078, op=MO_32) at ../accel/tcg/cputlb.c :1378

#11 0x0000555555bcb3d5 in store_helper (env=0x5555569448d0, addr=18446744073699054464, val=110440984, oi=34, retaddr=140736193352078, op=MO_32) at ../accel/tcg/cputlb.c :2397

#12 0x0000555555bcb64d in helper_le_stl_mmu (env=0x5555569448d0, addr=18446744073699054464, val=110440984, oi=34, retaddr=140736193352078) at ../accel/tcg/cputlb.c :2463

#13 0x00007fffb2cfd18e in code_gen_buffer ()

#14 0x0000555555b95552 in cpu_tb_exec (cpu=0x55555693c070, itb=0x7fffb306c500 <code_gen_buffer+12760275>) at ../accel/tcg/cpu-exec.c :178

#15 0x0000555555b96403 in cpu_loop_exec_tb (cpu=0x55555693c070, tb=0x7fffb306c500 <code_gen_buffer+12760275>, last_tb=0x7ffff504c5b8, tb_exit=0x7ffff504c5b0) at ../accel/tcg/cpu-exec.c :658

#16 0x0000555555b966fb in cpu_exec (cpu=0x55555693c070) at ../accel/tcg/cpu-exec.c :771

#17 0x0000555555bab751 in tcg_cpu_exec (cpu=0x55555693c070) at ../accel/tcg/tcg-cpus.c :243

#18 0x0000555555babcc2 in tcg_cpu_thread_fn (arg=0x55555693c070) at ../accel/tcg/tcg-cpus.c :427

#19 0x0000555555e77a29 in qemu_thread_start (args=0x55555696b890) at ../util/qemu-thread-posix.c :521

#20 0x00007ffff781b609 in start_thread (arg=<optimized out>) at pthread_create.c :477

#21 0x00007ffff773e353 in clone () at ../sysdeps/unix/sysv/linux/x86_64/clone.S :95或者重新启用某条时钟:qemu_clock_enable(type, true) 若从禁用变为启用 → qemu_clock_notify(type) → 遍历该时钟挂着的所有 QEMUTimerList 调 timerlist_notify()notify_cb(opaque)**。这种情景没有上一种常见。

timerlist_notify 函数定义如下:

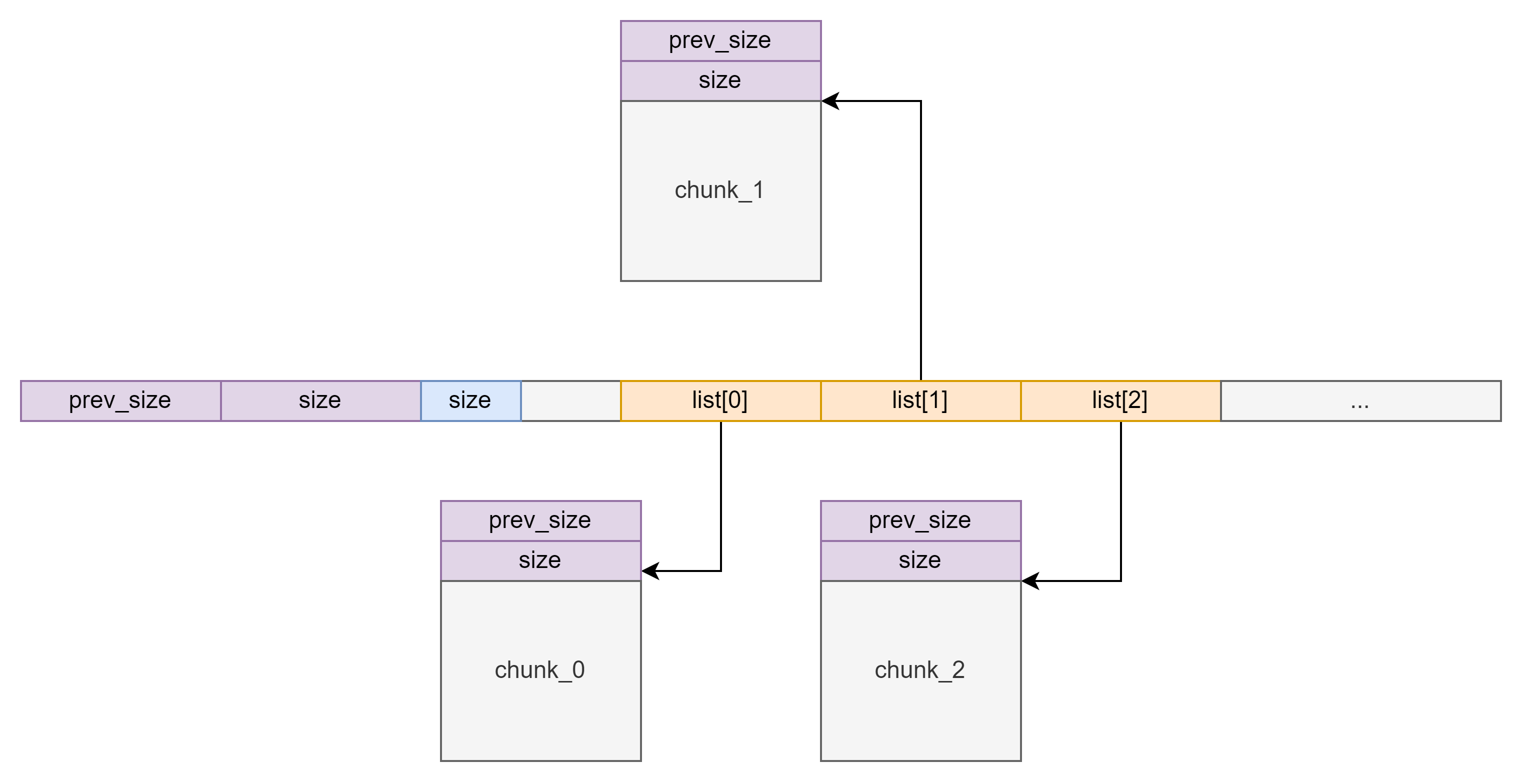

1 2 3 4 5 6 7 8 void timerlist_notify (QEMUTimerList *timer_list) { if (timer_list->notify_cb) { timer_list->notify_cb(timer_list->notify_opaque, timer_list->clock->type); } else { qemu_notify_event(); } }